1 registers, 1 registers -3, Table 19-1. watchdog timer register memory map -3 – Cirrus Logic EP93xx User Manual

Page 645

DS785UM1

19-3

Copyright 2007 Cirrus Logic

Watchdog Timer

EP93xx User’s Guide

1

9

1

9

19

Note: A software reset can reset the system without this register losing its contents.

19.1 Registers

Note: Watchdog registers are intended to be word-accessed only. Since the least significant

bytes of the address bus are not decoded, byte and half word accesses are not allowed

and may have unpredictable results.

Register Descriptions

Watchdog

Address:

0x8094_0000 - Read/Write

Default:

0x0000_0000

Definition:

Watchdog control register.

Bit Descriptions:

RSVD:

Reserved. Unknown during read.

WRITE ONLY BIT FIELDS

CTL:

Watchdog control bits. The ARM Core writes 0x5555 to

this half-word to periodically restart the watchdog timer.

Writing 0xAA55 to this hword will disable the watchdog

timer. Writing 0xAAAA to this hword will re-enable the

watchdog timer.

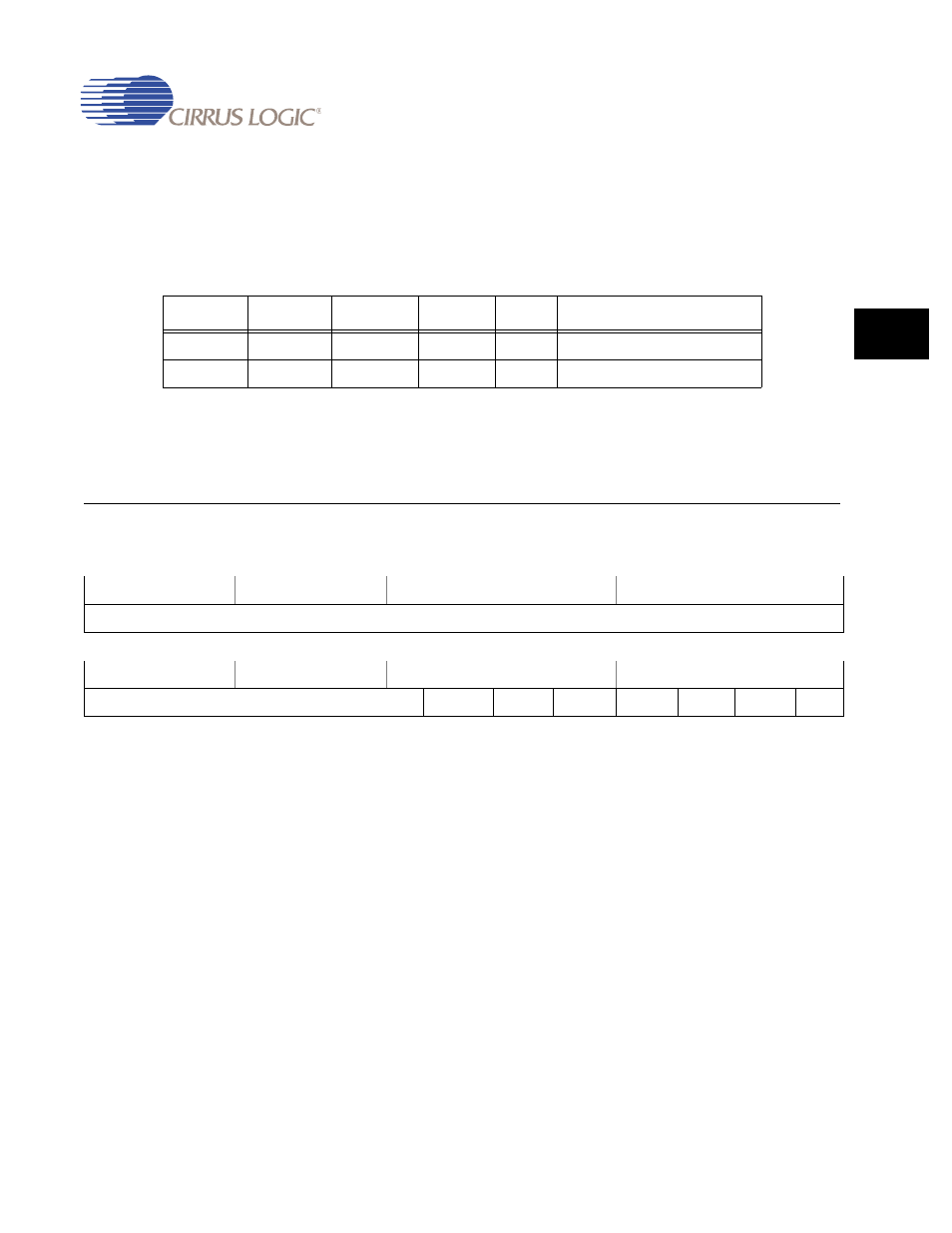

Table 19-1. Watchdog Timer Register Memory Map

Address

Name

SW locked

Type

Size

Description

0x8094_0000

No

Read/Write

16/3 bits

Watchdog Control Register

0x8094_0004

No

Read/Write

7 bits

Watchdog Status Storage Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CTL

CTL/PLSDSN

CTL/OVRID

CTL/SWDIS

CTL/HWDIS

CTL/URST

CTL/3KRST

CTL/WD