3 hardware configuration control, 3 hardware configuration control -2, Hardware configuration – Cirrus Logic EP93xx User Manual

Page 128

5-2

DS785UM1

Copyright 2007 Cirrus Logic

System Controller

EP93xx User’s Guide

5

5

5

certain system variables such as RTC, SDRAM refresh control/global configuration, and

the Syscon registers.

Note: If PLLs are enabled, user reset does NOT disable or reset the PLLs. They retain their

frequency settings.

•

Three-key reset. When F2, F4, and F7 are pressed, a user reset occurs.

•

Software reset and watchdog reset. They perform the functions of the user reset, but are

under software control.

registers contain the information

regarding which reset event occurred. Note that only the Watchdog timer contains

information about a user-generated 3-key reset.

5.1.3 Hardware Configuration Control

The Hardware Configuration controls provide a mechanism to place the system into various

boot configurations. In addition, one of several external boot memory options can be selected

at system wake up.

The Hardware Configuration controls are defined by a set of device pins that are latched into

configuration control bits on the rising edge of the PRSTn or RSTOn pin. The different

hardware configuration bits define watchdog behavior, boot mode (internal or external), boot

synchronicity, and external boot width. The latched pins are described in

.

The latched version of these signals have an “L” prefix, are stored in the SysCfg register, and

are readable by software. Note that the signals EECLK and EEDAT may have 1 k

Ω

pull-up

resisters if used in an open-drain two-wire serial port application. (The default state

assignments will assume these pull-ups.)

The Hardware Control configurations are show in

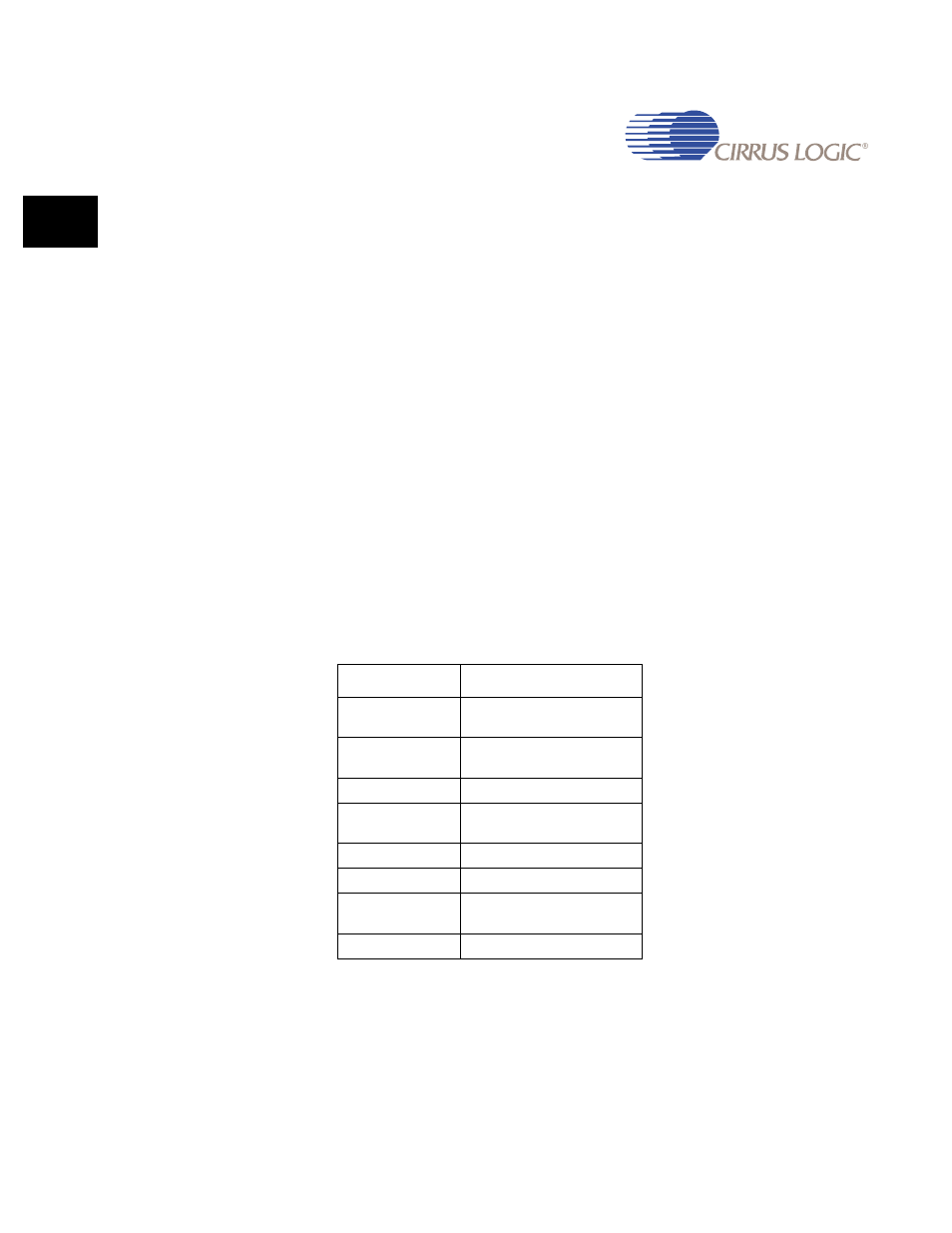

Table 5-1. Hardware Configuration Control Latched Pins

Pin Name(s)

Action

CSn[1]

Enable/Disable Watchdog

reset timer

CSn[2]

Enable/Disable Watchdog

reset duration

CSn[3]

Should be pulled-up to “1”

EECLK

Select internal or external

boot

EEDAT

Should be pulled-up to “1”

BOOT[1:0]

Select boot mode

ASDO

Select synchronous or

asynchronous boot

CSn[7:6]

Select external boot width