4 gpio pin map, 4 gpio pin map -6, Table 28-2. ep9307 gpio port to pin map -6 – Cirrus Logic EP93xx User Manual

Page 796

28-6

DS785UM1

Copyright 2007 Cirrus Logic

GPIO Interface

EP93xx User’s Guide

2

8

2

8

28

28.1.4 GPIO Pin Map

All GPIO signals are mapped to device pins. The Syscon DeviceCfg register contains four

bits that control mapping of the GPIO Ports to device pins: GonK, EonIDE, GonIDE, and

HonIDE.

,

show how the GPIO ports map

to EP93xx pins depending on these control signals.

1. GRLED is the Green LED pin.

2. RDLED is the Red LED pin.

3. EECLK is the EEPROM clock pin.

4. EEDAT is the EEPROM data pin.

1. GRLED is the Green LED pin.

2. RDLED is the Red LED pin.

3. EECLK is the EEPROM clock pin.

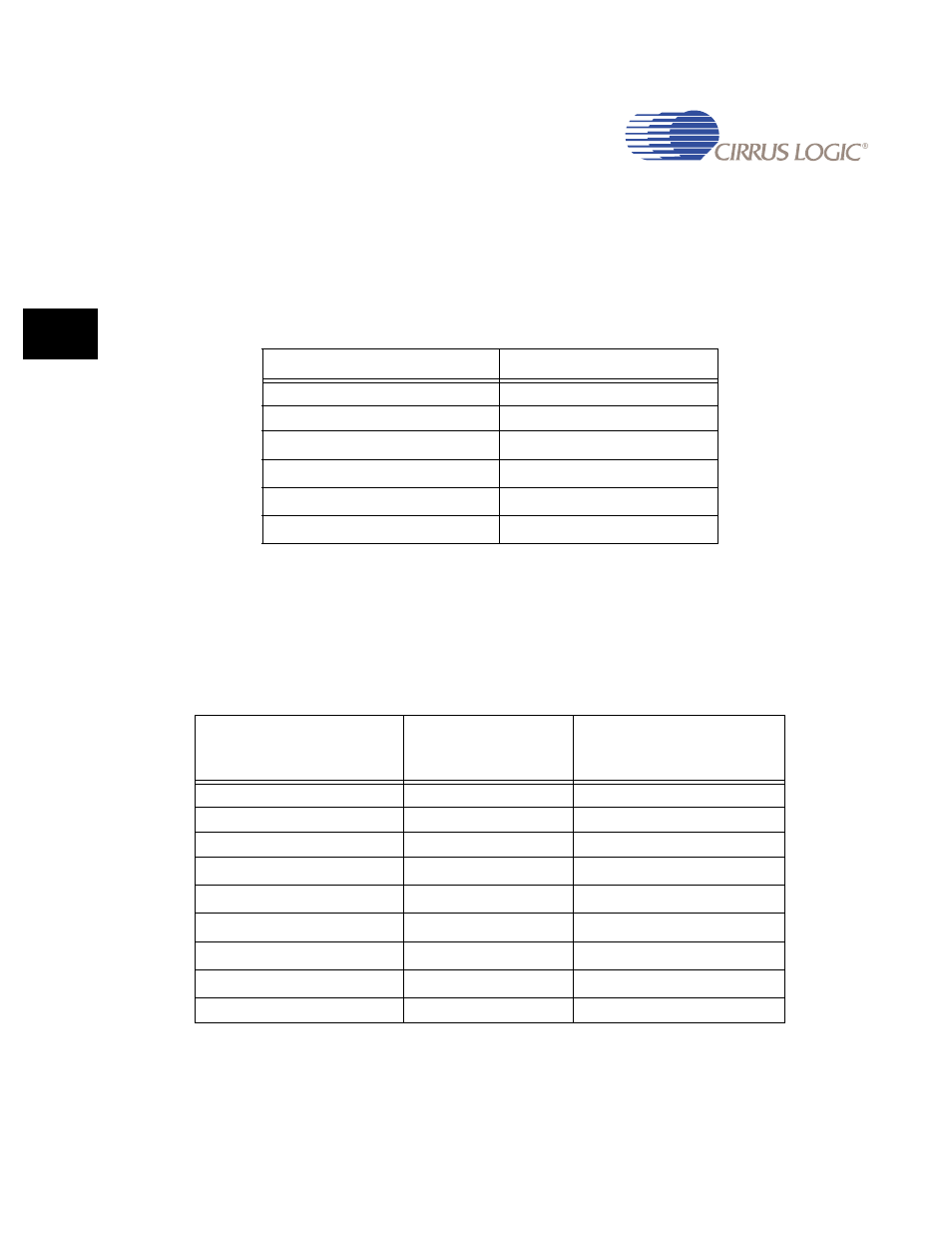

Table 28-1. EP9301 and EP9302 GPIO Port to Pin Map

Pin Name

Default Function

EGPIO[7:0]

Port A

EGPIO[15:8]

Port B

GRLED

1

Port E0

RDLED

2

Port E1

EECLK

3

Port G0

EEDAT

4

Port G1

Table 28-2. EP9307 GPIO Port to Pin Map

Pin

Name

Default

Function

Function in

GonK

Mode

EGPIO[7:0] Port

A

Port

A

EGPIO[13:8] Port

B

Port

B

EGPIO[15] Port

B

Port

B

GRLED

1

Port E0

Port E0

RDLED

2

Port E1

Port E1

EECLK

3

Port G0

Port G0

EEDAT

4

Port G1

Port G1

ROW[7:0]

5

ROW[7:0]

Port C

COL[7:0]6

COL[7:0]

Port D