Cirrus Logic EP93xx User Manual

Page 155

DS785UM1

5-29

Copyright 2007 Cirrus Logic

System Controller

EP93xx User’s Guide

5

5

5

SWRST:

Software reset. A one to zero transition of this bit initiates

a software reset.

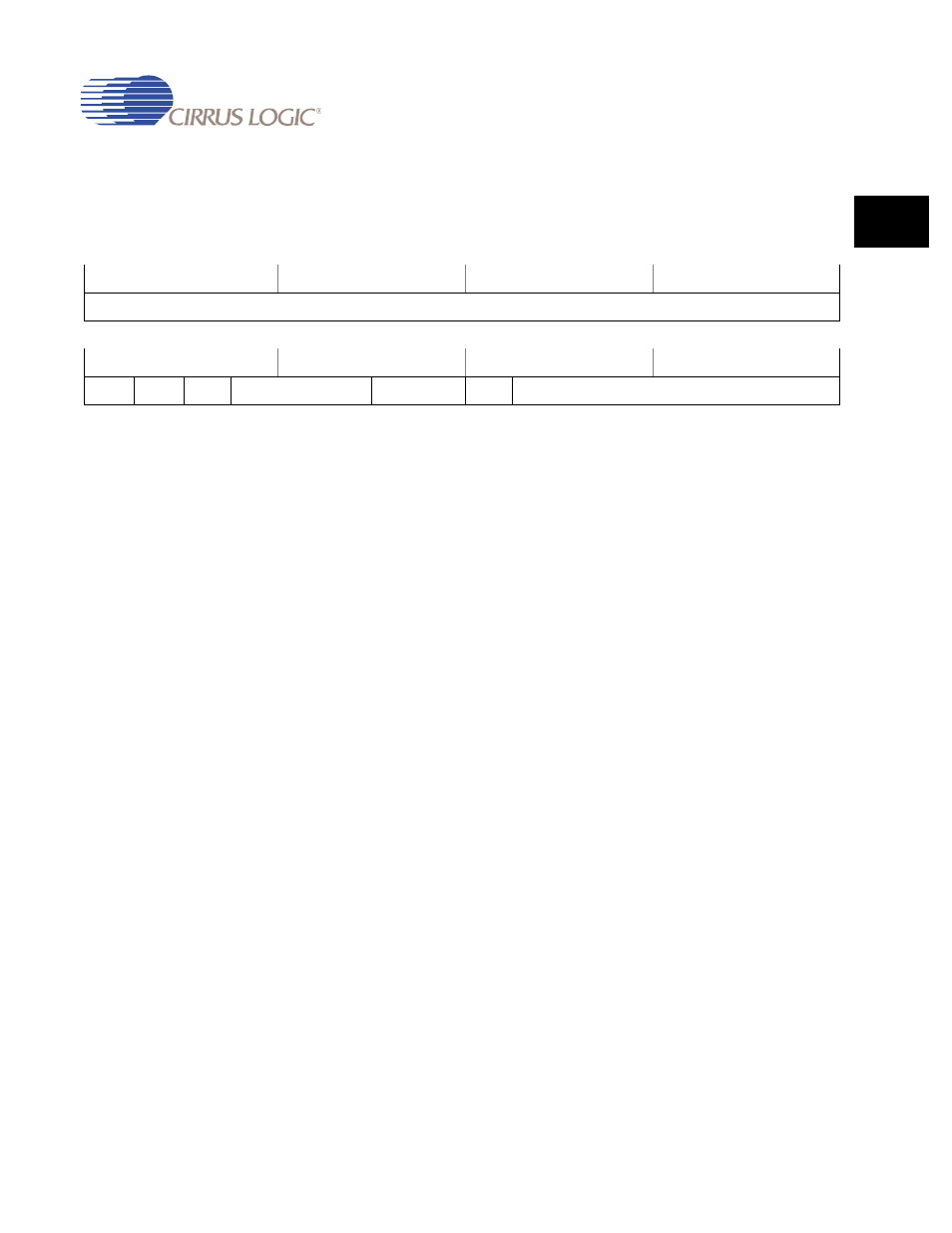

VidClkDiv

Address:

0x8093_0084 - Read/Write, Software locked

Default:

0x0000_0000

Definition:

Configures video clock for the raster engine. Selects input to VCLK dividers

from either PLL1 or PLL2, and defines a programmable divide value.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

VENA:

Enable VCLK divider.

ESEL:

External clock source select.

0 - use the external XTALI clock input as the clock source.

1 - use one of the internal PLLs selected by PSEL as the

clock source.

PSEL:

PLL source select.

1 - select PLL2 as the clock source.

0 - select PLL1 as the clock source.

PDIV:

Pre-divider value. Generates divide by 2, 2.5, or 3 from the

clock source.

00 - Disable clock

01 - Divide-by-2

10 - Divide-by-2.5

11 - Divide-by-3

VDIV:

VCLK divider value. Forms a divide-by-N of the pre-divide

clock output. VCLK is the source clock divided by PDIV

divided by N. Must be at least two.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

VENA

ESEL

PSEL

RSVD

PDIV

RSVD

VDIV