Cirrus Logic EP93xx User Manual

Page 695

DS785UM1

22-7

Copyright 2007 Cirrus Logic

AC’97 Controller

EP93xx User’s Guide

2

2

2

2

22

Address:

AC97DR1 - 0x8088_0000 - Read/Write

AC97DR2 - 0x8088_0020 - Read/Write

AC97DR3 - 0x8088_0040 - Read/Write

AC97DR4 - 0x8088_0060 - Read/Write

Definition:

The AC97DR registers are read / write data registers that are normally 20 bits

wide. In 16-bit compact mode, all 32 available bits are used. This register is

zero at reset.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

DATA:

Write - Transmit FIFO: The AC97TXCR register qualifies

the data within the TX FIFO.

Read - Receive FIFO: The AC97RXCR register qualifies

the data within the FIFO.

For words to be transmitted:

•

If the FIFOs are enabled, data written to this location is pushed onto the transmit FIFO.

•

If the FIFOs are not enabled, data is stored in the transmitter holding register (the bottom

word of the transmit FIFO).

For received words:

•

If the FIFOs are enabled, the data received is pushed onto the receive FIFO.

•

If the FIFOs are not enabled, the data received is stored in the receiving holding register

(the bottom word of the receive FIFO).

The receive FIFO is 21 bits wide. The 21

st

bit, the receive overrun error status, can only be

read via the AC97ISR registers. The receive overrun error status bit is transferred down to

the FIFO buffer along with the overrun data value.

AC97RXCRx

Address:

AC97RXCR1 - 0x8088_0004 - Read/Write

AC97RXCR2 - 0x8088_0024 - Read/Write

AC97RXCR3 - 0x8088_0044 - Read/Write

AC97RXCR4 - 0x8088_0064 - Read/Write

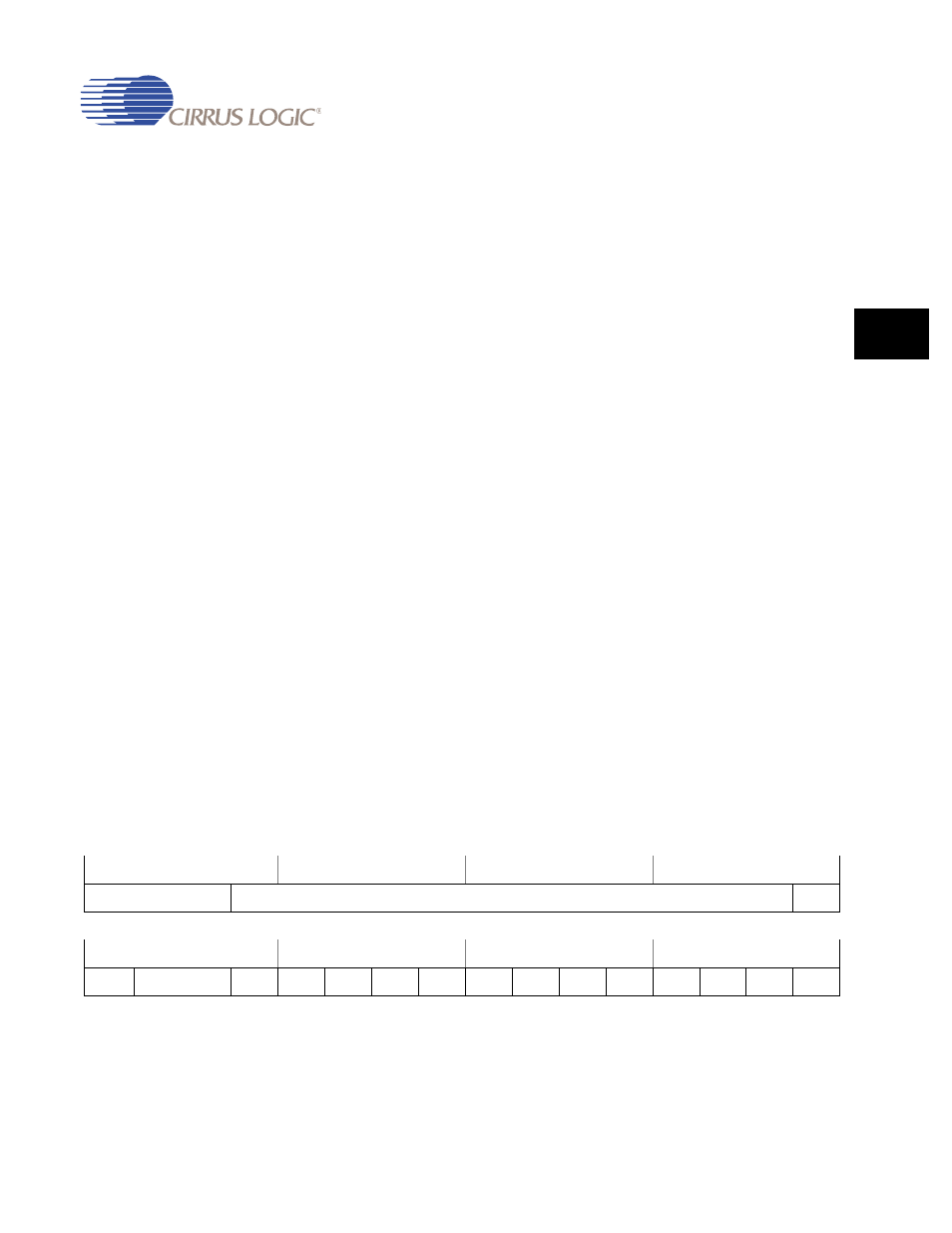

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

TOC

FDIS

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CM

RSIZE

RX12

RX11

RX10

RX9

RX8

RX7

RX6

RX5

RX4

RX3

RX2

RX1

REN