Cirrus Logic EP93xx User Manual

Page 567

DS785UM1

15-9

Copyright 2007 Cirrus Logic

UART2

EP93xx User’s Guide

1

5

1

5

15

FE:

Framing Error. When this bit is set to “1”, it indicates that

the received character did not have a valid stop bit (a valid

stop bit is “1”). This bit is cleared to 0 by a write to

UART2RXSts. In FIFO mode, this error is associated with

the character at the top of the FIFO.

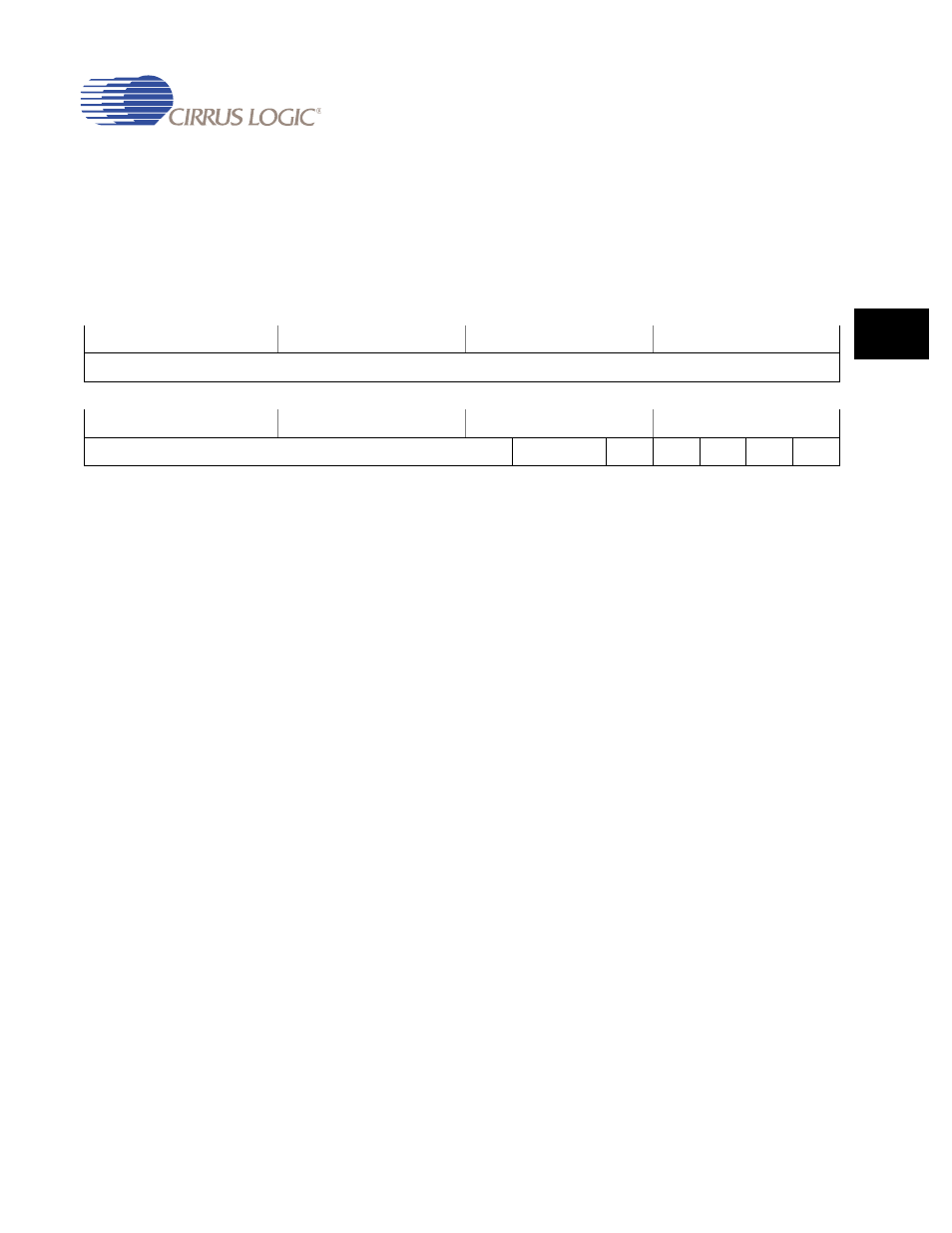

UART2LinCtrlHigh

Address:

0x808D_0008 - Read/Write

Default:

0x0000_0000

Definition:

UART - High. UART2LinCtrlHigh, UART2LinCtrlMid and UART2LinCtrlLow

form a single 23-bit wide register (UART2LinCtrl) which is updated on a single

write strobe generated by an UART2LinCtrlHigh write. So, in order to internally

update the contents of UART2LinCtrlMid or UART2LinCtrlLow, a

UART2LinCtrlHigh write must always be performed at the end.

To update the three registers there are two possible sequences:

• UART2LinCtrlLow write, UART2LinCtrlMid write and UART2LinCtrlHigh write

• UART2LinCtrlMid write, UART2LinCtrlLow write and UART2LinCtrlHigh

write.

To update UART2LinCtrlLow or UART2LinCtrlMid only:

•

UART2LinCtrlLow write (or UART2LinCtrlMid write) and UART2LinCtrlHigh

write.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

WLEN:

Number of bits per frame:

11 = 8 bits

10 = 7 bits

01 = 6 bits

00 = 5 bits

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

WLEN

FEN

STP2

EPS

PEN

BRK