Cirrus Logic EP93xx User Manual

Page 682

21-26

DS785UM1

Copyright 2007 Cirrus Logic

I

2

S Controller

EP93xx User’s Guide

2

1

2

1

21

I

2

S Configuration and Status Register Descriptions

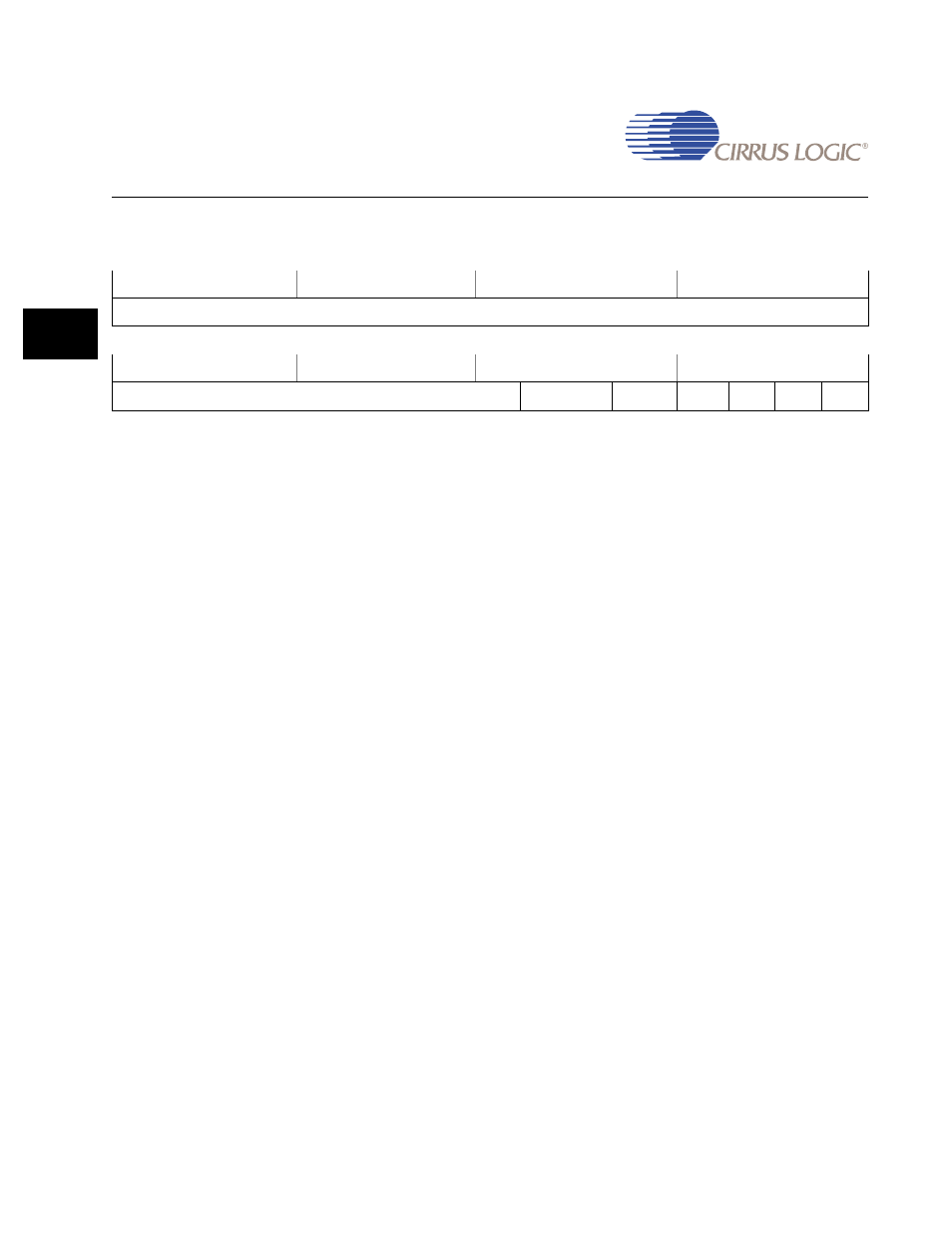

I2STXClkCfg

Address:

0x8082_0000 - Read/Write

Default

0x0000_0000

Definition:

Transmitter clock configuration register.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

i2s_tx_bcr:

Defines the TX bit clock rate.

00 - I2STXClkCfg[4] defines the bit clock generation.

01 - Bit clock rate is fixed at 32x. Word length is ignored.

10 - Bit clock rate is fixed at 64x. Word length is ignored.

11 - Bit clock rate is fixed at 128x. Word length is ignored.

i2s_tx_nbcg:

Defines TX not bit clock gating mode.

If I2STXClkCfg[5:6] = 00, this bit defines the bit clock rate,

otherwise ignored.

Bit clock rate = 32x if word length is 16.

Bit clock rate = 64x if word length is 32.

Bit clock rate = 64x if word length is 24.

There is a special case when the word length is 24.

If this bit = 0 and the word length is 24, the last 8 cycles

are gated off in each word.

If this bit = 1 and the word length is 24, the last 8 cycles

are not gated off in each word.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

i2s_tx_bcr

i2s_tx_nbcg

i2s_mstr

i2s_trel

i2s_tckp

i2s_tlrs