Cirrus Logic EP93xx User Manual

Page 65

DS785UM1

2-27

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

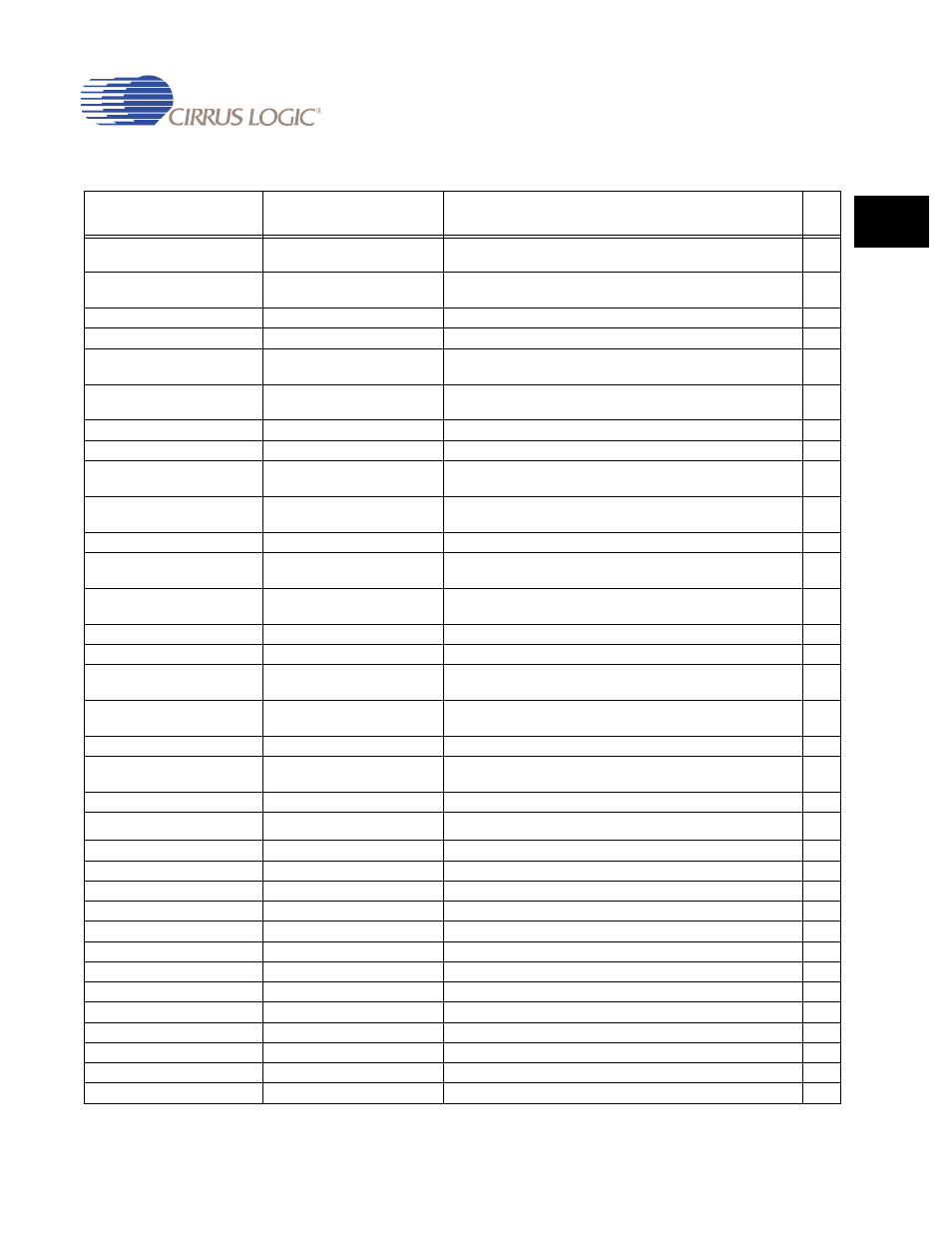

0x8084_005C IntStsF

GPIO Interrupt Status Register. Contains status of Port F

interrupts after masking.

N

0x8084_0060 RawIntStsF

Raw Interrupt Status Register. Contains raw interrupt status of

Port F before masking.

N

0x8084_0064

GPIOFDB

GPIO F Debounce Register

N

0x8084_0068 - 0x8084_008C

Reserved

0x8084_0090 GPIOAIntType1

Register controlling type, level or edge, of interrupt generated by

the pins of Port A

N

0x8084_0094 GPIOAIntType2

Register controlling polarity, high/low or rising/falling, of interrupt

generated by Port A

N

0x8084_0098

GPIOAEOI

GPIO Port A End Of Interrupt Register

N

0x8084_009C

GPIOAIntEn

Controlling the generation of interrupts by the pins of Port A

N

0x8084_00A0 IntStsA

GPIO Interrupt Status Register. Contains status of Port A

interrupts after masking.

N

0x8084_00A4 RawIntStsA

Raw Interrupt Status Register. Contains raw interrupt status of

Port A before masking.

N

0x8084_00A8

GPIOADB

GPIO A Debounce Register

N

0x8084_00AC GPIOBIntType1

Register controlling type, level or edge, of interrupt generated by

the pins of Port B

N

0x8084_00B0 GPIOBIntType2

Register controlling polarity, high/low or rising/falling, of interrupt

generated by Port B

N

0x8084_00B4

GPIOBEOI

GPIO Port B End Of Interrupt Register

N

0x8084_00B8

GPIOBIntEn

Controlling the generation of interrupts by the pins of Port B

N

0x8084_00BC IntStsB

GPIO Interrupt Status Register. Contains status of Port B

interrupts after masking.

N

0x8084_00C0 RawIntStsB

Raw Interrupt Status Register. Contains raw interrupt status of

Port B before masking.

N

0x8084_00C4

GPIOBDB

GPIO B Debounce Register

N

0x8084_00C8 EEDrive

EEPROM pin drive type control. Defines the driver type for the

EECLK and EEDAT pins

N

0x8088_xxxx

AC’97

AC’97 Control Registers

0x8088_0000

AC97DR1

Data read or written from/to FIFO1

N

0x8088_0004

AC97RXCR1

Control Register for receive

N

0x8088_0008

AC97TXCR1

Control Register for transmit

N

0x8088_000C

AC97SR1

Status Register

N

0x8088_0010

AC97RISR1

Raw interrupt status Register

N

0x8088_0014

AC97ISR1 Interrupt

Status

N

0x8088_0018

AC97IE1 Interrupt

Enable

N

0x8088_001C

Reserved

0x8088_0020

AC97DR2

Data read or written from/to FIFO2

N

0x8088_0024

AC97RXCR2

Control Register for receive

N

0x8088_0028

AC97TXCR2

Control Register for transmit

N

0x8088_002C

AC97SR2 Status

Register

N

0x8088_0030

AC97RISR2

Raw interrupt status Register

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock