Cirrus Logic EP93xx User Manual

Page 69

DS785UM1

2-31

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

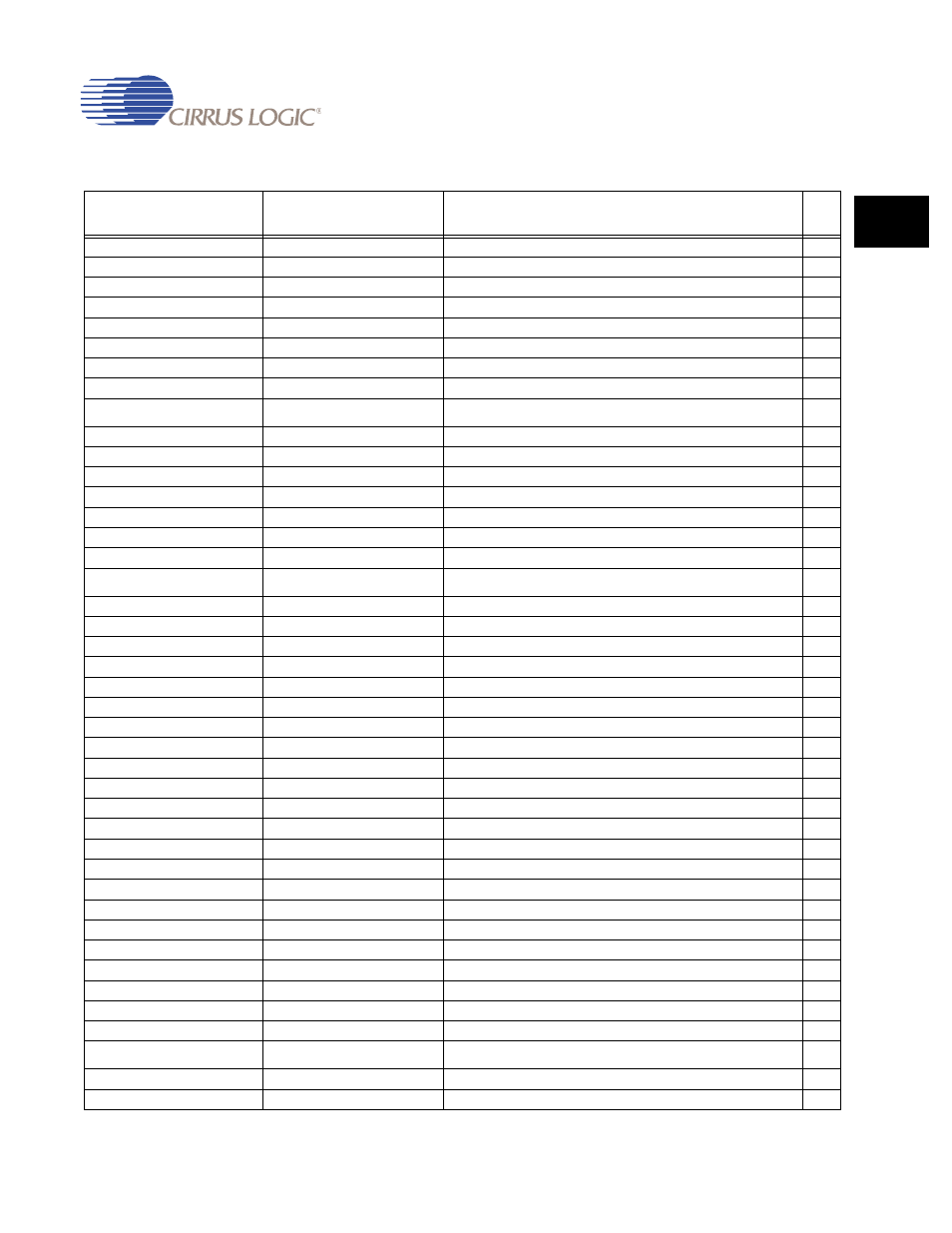

0x8091_000C

PWM0Invert

PWM0 Invert

N

0x8091_0010

PWM0Sync

PWM0 Synchronous

N

0x8091_0020

PWM1_TC

PWM1 Terminal Count

N

0x8091_0024

PWM1_DC

PWM1 Duty Cycle

N

0x8091_0028

PWM1_EN

PWM1 Enable

N

0x8091_002C

PWM1_INV

PWM1 Invert

N

0x8091_0030

PWM1_SYNC

PWM1 Synchronous

N

0x8092_xxxx

RTC

RTC Control Registers

0x8092_0000

RTCData

RTC Data Register

N

0x8092_0004

RTCMatch

RTC Match Register

N

0x8092_0008

RTCSts

RTC Status/EOI Register

N

0x8092_000C

RTCLoad

RTC Load Register

N

0x8092_0010

RTCCtrl

RTC Control Register

N

0x8092_0098

RTCSWComp

RTC Software Compensation

N

0x8093_xxxx

Syscon

System Control Registers

0x8093_0000

PwrSts

Power/state control state

N

0x8093_0004

PwrCnt

Clock/debug control status

N

0x8093_0008

Halt

Enter IDLE mode

N

0x8093_000C

Stby

Enter Standby mode

N

0x8093_0018

TEOI

Write to clear Watchdog interrupt

N

0x8093_001C

STFClr

Write to clear Nbflg, rstflg, pfflg and cldflg

N

0x8093_0020

ClkSet1

Clock speed control 1

N

0x8093_0024

ClkSet2

Clock speed control 2

N

0x8093_0040

ScratchReg0

Scratch Register 0

N

0x8093_0044

ScratchReg1

Scratch Register 1

N

0x8093_0050

APBWait

APB wait

N

0x8093_0054

BusMstrArb

Bus Master Arbitration

N

0x8093_0058

BootModeClr

Boot Mode Clear Register

N

0x8093_0080

DeviceCfg

Device configuration

Y

0x8093_0084

VidClkDiv

Video Clock Divider

Y

0x8093_0088

MIRClkDiv

MIR Clock Divider. Configures video clock for the raster engine.

Y

0x8093_008C

I2SClkDiv

I2S Audio Clock Divider

0x8093_0090

KeyTchClkDiv

Keyscan/Touch Clock Divider

Y

0x8093_0094

ChipID

Chip ID Register

Y

0x8093_009C

SysCfg

System Configuration

Y

0x8093_00C0

SysSWLock

Syscon Software Lock Register

N

0x8094_xxxx

WATCHDOG

Watchdog Control Register

N

0x8094_0000

Watchdog

Watchdog Timer Register

N

0x8094_0004

WDStatus

Watchdog Status Register

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock