Cirrus Logic EP93xx User Manual

Page 585

DS785UM1

16-9

Copyright 2007 Cirrus Logic

UART3 With HDLC Encoder

EP93xx User’s Guide

1

6

1

6

16

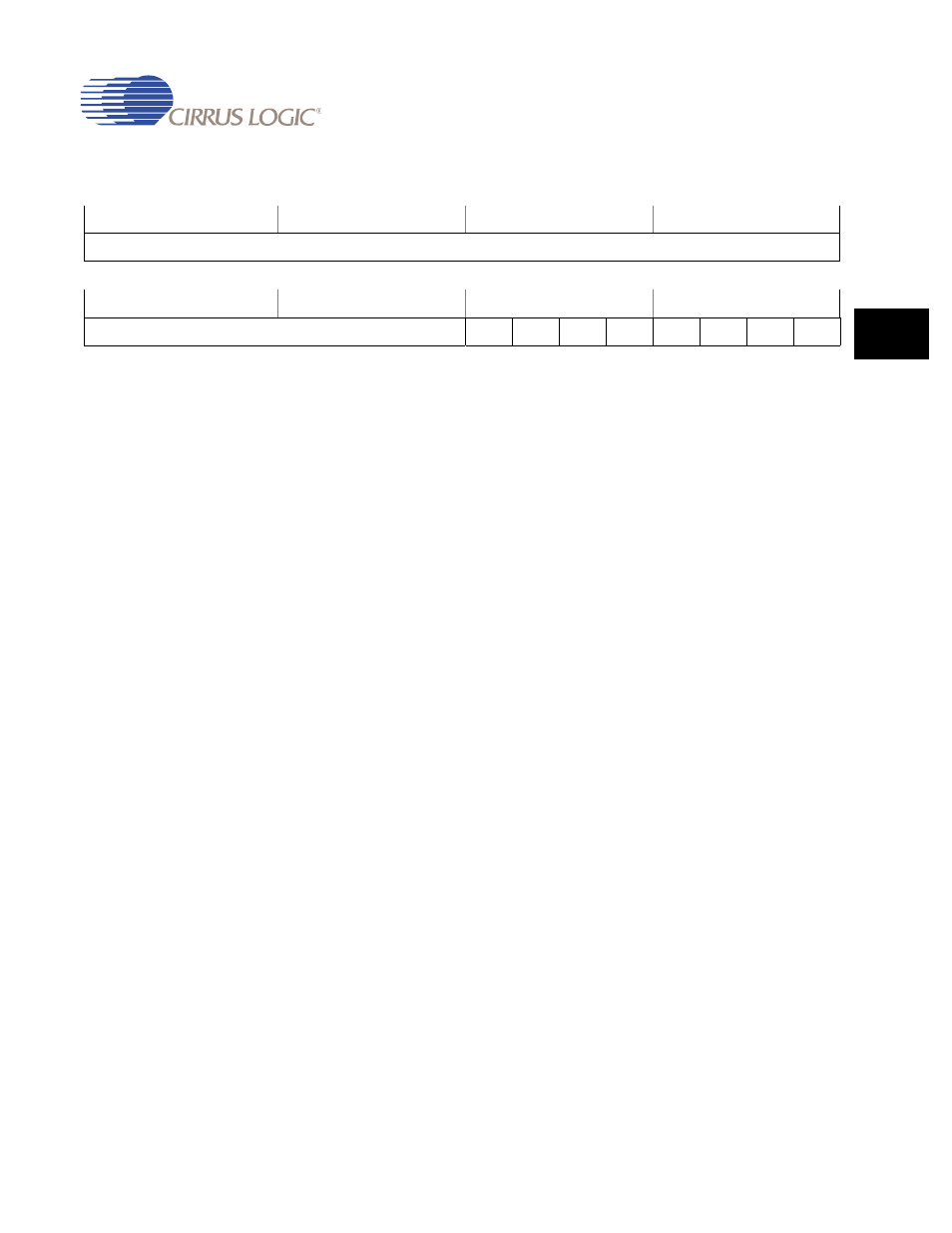

UART3Flag

Address:

0x808E_0018 - Read/Write

Default:

0x0000_0000

Definition:

UART3 Flag Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

TXFE:

Transmit FIFO Empty. The meaning of this bit depends on

the state of the FEN bit in the UART3LinCtrlHigh register.

If the FIFO is disabled, this bit is set when the transmit

holding register is empty. If the FIFO is enabled, the TXFE

bit is set when the transmit FIFO is empty.

RXFF:

Receive FIFO Full. The meaning of this bit depends on the

state of the FEN bit in the UART3LinCtrlHigh register. If

the FIFO is disabled, this bit is set when the receive

holding register is full. If the FIFO is enabled, the RXFF bit

is set when the receive FIFO is full.

TXFF:

Transmit FIFO Full. The meaning of this bit depends on

the state of the FEN bit in the UART3LinCtrlHigh register.

If the FIFO is disabled, this bit is set when the transmit

holding register is full. If the FIFO is enabled, the TXFF bit

is set when the transmit FIFO is full.

RXFE:

Receive FIFO Empty. The meaning of this bit depends on

the state of the FEN bit in the UART3LinCtrlHigh register.

If the FIFO is disabled, this bit is set when the receive

holding register is empty. If the FIFO is enabled, the RXFE

bit is set when the receive FIFO is empty.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

TXFE

RXFF

TXFF

RXFE

BUSY

DCD

DSR

CTS