2 interrupt configuration, 2 interrupt configuration -3, Table 6-1. interrupt configuration -3 – Cirrus Logic EP93xx User Manual

Page 165

DS785UM1

6-3

Copyright 2007 Cirrus Logic

Vectored Interrupt Controller

EP93xx User’s Guide

6

6

6

Any 16 of the 32 interrupts (per VIC) can be designated as ‘vectored’ by programming the

Vector address registers,

and the Vector Control registers,

An interrupt is designated as either IRQ or FIQ by programming the

register.

The IRQ and FIQ request logic has an asynchronous path. This allows interrupts to be

asserted when the clock is disabled.

Software can generate a specific interrupt by writing a ‘1’ to the associated bit in the

register.

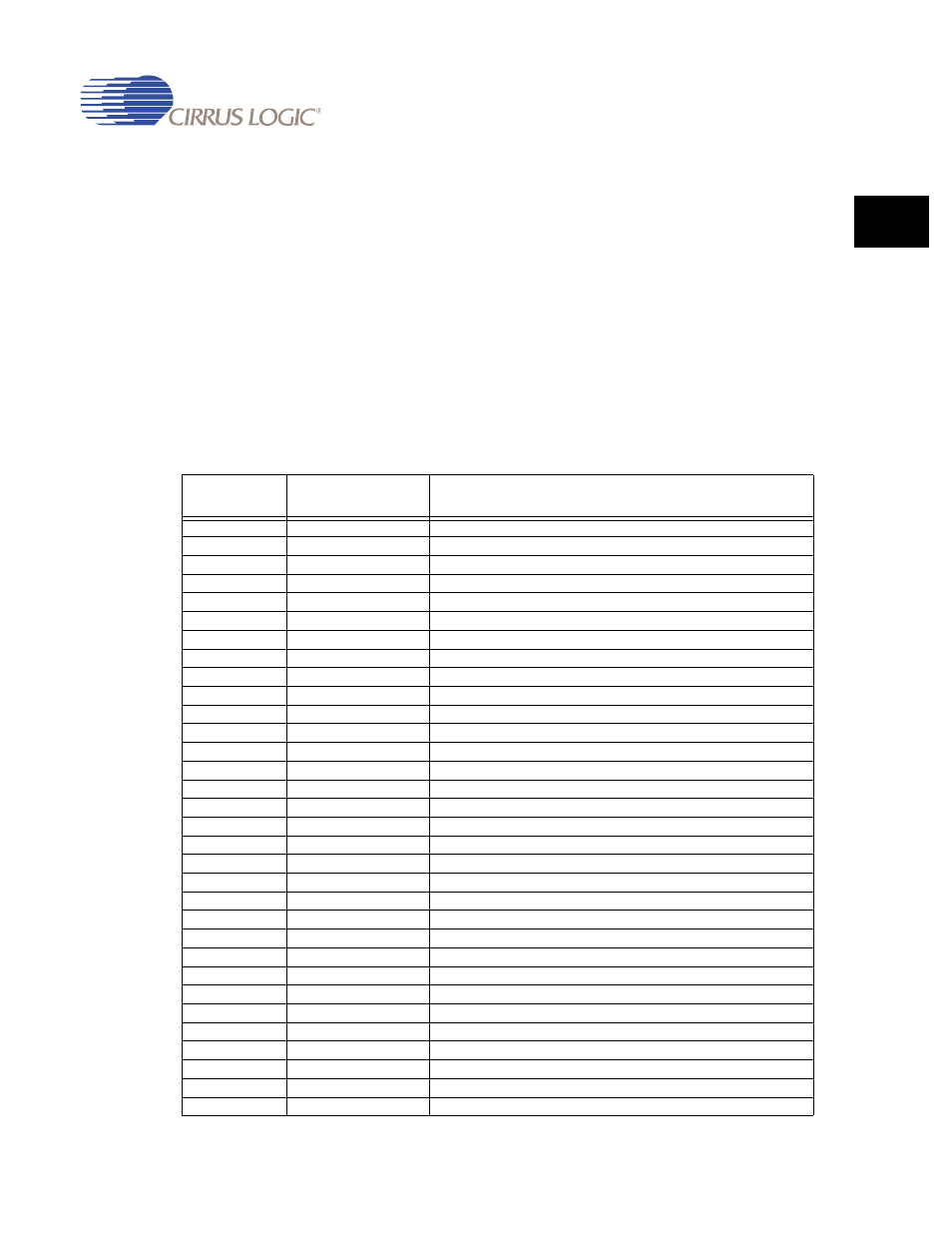

6.1.2 Interrupt Configuration

shows Interrupt Configuration.

Table 6-1. Interrupt Configuration

VIC Interrupt

Source

Name

Description

0

-

Unused

1

-

Unused

2

COMMRX

ARM Communication Rx for Debug

3

COMMTX

ARM Communication Tx for Debug

4

TC1UI

TC1 under flow interrupt (Timer Counter 1)

5

TC2UI

TC2 under flow interrupt (Timer Counter 2)

6

AACINTR

Advanced Audio Codec interrupt

7

DMAM2P0

DMA Memory to Peripheral Interrupt 0

8

DMAM2P1

DMA Memory to Peripheral Interrupt 1

9

DMAM2P2

DMA Memory to Peripheral Interrupt 2

10

DMAM2P3

DMA Memory to Peripheral Interrupt 3

11

DMAM2P4

DMA Memory to Peripheral Interrupt 4

12

DMAM2P5

DMA Memory to Peripheral Interrupt 5

13

DMAM2P6

DMA Memory to Peripheral Interrupt 6

14

DMAM2P7

DMA Memory to Peripheral Interrupt 7

15

DMAM2P8

DMA Memory to Peripheral Interrupt 8

16

DMAM2P9

DMA Memory to Peripheral Interrupt 9

17

DMAM2M0

DMA Memory to Memory Interrupt 0

18

DMAM2M1

DMA Memory to Memory Interrupt 1

19

-

Reserved

20

-

Reserved

21

-

Reserved

22

-

Reserved

23

UART1RXINTR1

UART 1 Receive Interrupt

24

UART1TXINTR1

UART 1 Transmit Interrupt

25

UART2RXINTR2

UART 2 Receive Interrupt

26

UART2TXINTR2

UART 2 Transmit Interrupt

27

UART3RXINTR3

UART 3 Receive Interrupt

28

UART3TXINTR3

UART 3 Transmit Interrupt

29

INT_KEY

Keyboard Matrix Interrupt

30

INT_TOUCH

Touch Screen Controller Interrupt

31

-

Reserved