5 frame buffer memory size, 6 pulse width modulated brightness – Cirrus Logic EP93xx User Manual

Page 188

7-6

DS785UM1

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

7.3.5 Frame Buffer Memory Size

Several screens may be available for video display depending on screen size, pixel depth,

and amount of memory dedicated to video images. The screen size can be up to 1280 x 1024

pixels, the pixel depth can be 4 bpp, 8 bpp, 16 bpp, 24 bpp packed, or 32 bpp (24 bpp

unpacked).

7.3.6 Pulse Width Modulated Brightness

The circuitry provides a pulse width modulated brightness control output, Bright, that can be

used in conjunction with an external resistor and capacitor to provide a DC voltage level for

Pixel 3 Red

Pixel 3 Green

Pixel 3 Blue

Pixel 2 Red

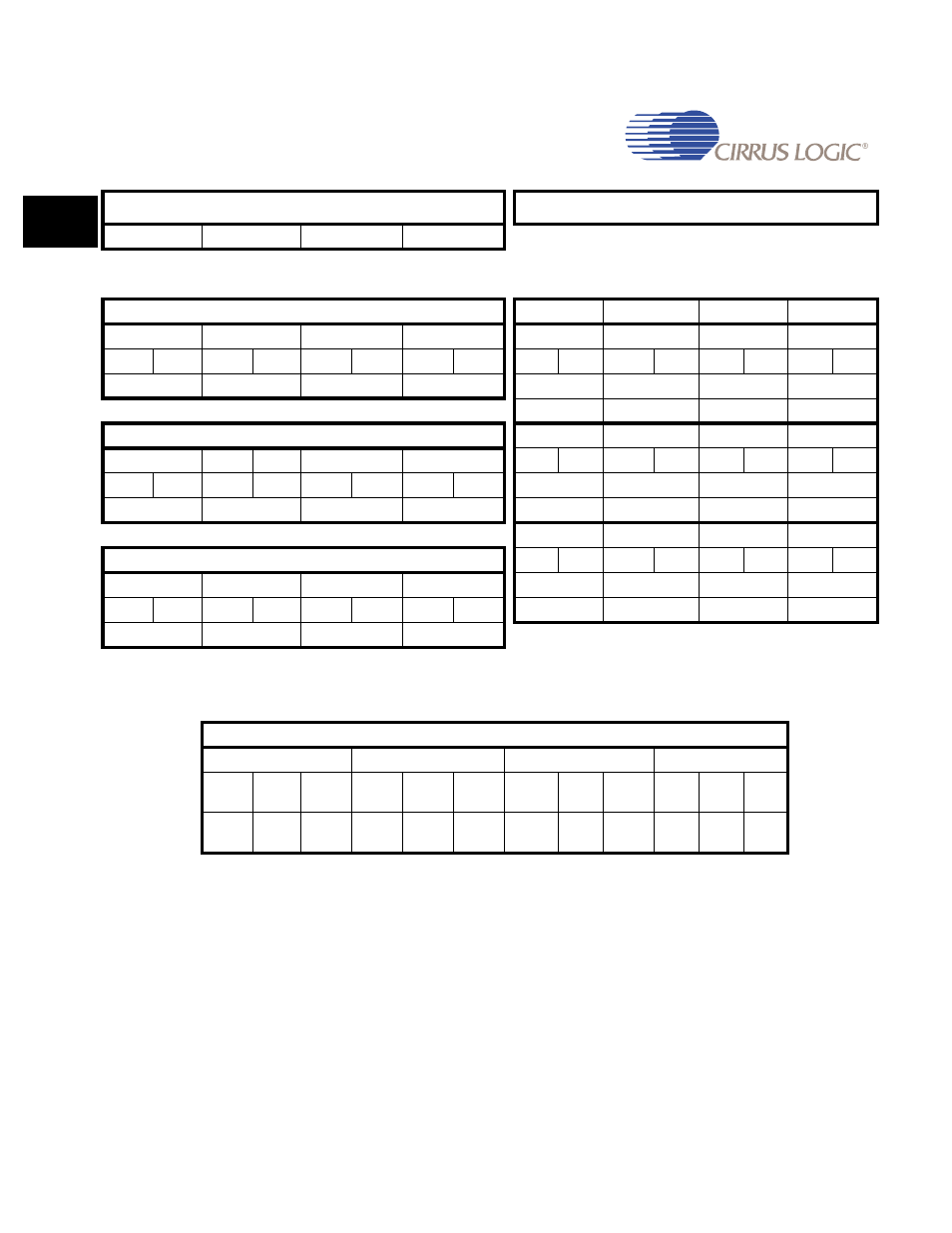

32 bits per pixel (24 bits per pixel unpacked)

32-bit Word 0

Pixel 0

Pixel 1

Pixel 2

Pixel 3

Byte 3

Byte 2

Byte 1

Byte 0

Red

Red

Red

Red

bit 31

bit 24

bit 23

bit 16

bit 15

bit 8

bit 7

bit 0

bit 23

bit 16

bit 23

bit 16

bit 23

bit 16

bit 23

bit 16

Unused

Pixel 0 Red

Pixel 0 Green

Pixel 0 Blue

Byte 2

Byte 6

Byte B

Byte E

Word 0

Word 1

Word 2

Word 3

32-bit Word 1

Green

Green

Green

Green

Byte 7

Byte 6

Byte 5

Byte 4

bit 15

bit 8

bit 15

bit 8

bit 15

bit 8

bit 15

bit 8

bit 31

bit 24

bit 23

bit 16

bit 15

bit 8

bit 7

bit 0

Byte 1

Byte 5

Byte A

Byte D

Unused

Pixel 1 Red

Pixel 1 Green

Pixel 1 Blue

Word 0

Word 1

Word 2

Word 3

Blue

Blue

Blue

Blue

32-bit Word 2

bit 7

bit 0

bit 7

bit 0

bit 7

bit 0

bit 7

bit 0

Byte B

Byte A

Byte 9

Byte 8

Byte 0

Byte 4

Byte 8

Byte C

bit 31

bit 24

bit 23

bit 16

bit 15

bit 8

bit 7

bit 0

Word 0

Word 1

Word 2

Word 3

Unused

Pixel 2 Red

Pixel 2 Green

Pixel 2 Blue

Compressed images for remapping

1 bit per pixel

32-bit Word

Byte 3

Byte 2

Byte1

Byte 0

bit 31

bit 24

bit 23

bit 16

bit 15

bit 8

bit 7

bit 0

Pixel

24

Pixel

31

Pixel

16

Pixel

23

Pixel 8

Pixel

15

Pixel

0

Pixel

7

Table 7-2. Byte Oriented Frame Buffer Organization (Continued)

As stored in memory

In pixel output order (progressive scan)