Cirrus Logic EP93xx User Manual

Page 572

15-14

DS785UM1

Copyright 2007 Cirrus Logic

UART2

EP93xx User’s Guide

1

5

1

5

15

RXFF:

Receive FIFO Full. The meaning of this bit depends on the

state of the FEN bit in the UART2LinCtrlHigh register. If

the FIFO is disabled, this bit is set when the receive

holding register is full. If the FIFO is enabled, the RXFF bit

is set when the receive FIFO is full.

TXFF:

Transmit FIFO Full. The meaning of this bit depends on

the state of the FEN bit in the UART2LinCtrlHigh register.

If the FIFO is disabled, this bit is set when the transmit

holding register is full. If the FIFO is enabled, the TXFF bit

is set when the transmit FIFO is full.

RXFE:

Receive FIFO Empty. The meaning of this bit depends on

the state of the FEN bit in the UART2LinCtrlHigh register.

If the FIFO is disabled, this bit is set when the receive

holding register is empty. If the FIFO is enabled, the RXFE

bit is set when the receive FIFO is empty.

BUSY:

UART Busy. If this bit is set to “1”, the UART is busy

transmitting data. This bit remains set until the complete

byte, including all the stop bits, has been sent from the

shift register. This bit is set as soon as the transmit FIFO

becomes non-empty (regardless of whether the UART is

enabled or not).

DCD:

Data Carrier Detect status. This bit is the complement of

the UART data carrier detect (nUARTDCD) modem status

input. That is, the bit is “1” when the modem status input is

0.

DSR:

Data Set Ready status. This bit is the complement of the

UART data set ready (nUARTDSR) modem status input.

That is, the bit is “1” when the modem status input is 0.

CTS:

Clear To Send status. This bit is the complement of the

UART clear to send (nUARTCTS) modem status input.

That is, the bit is “1” when the modem status input is 0.

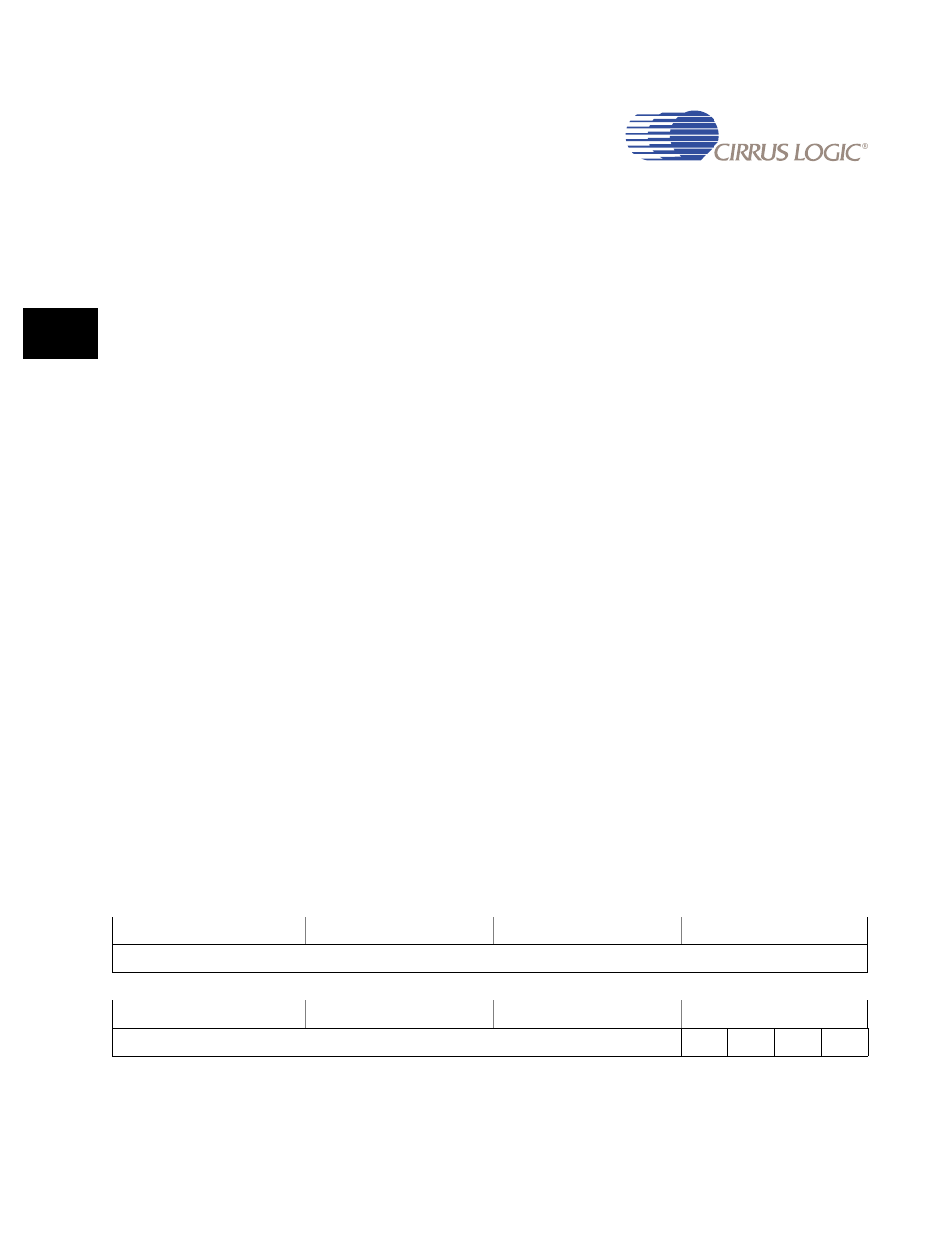

UART2IntIDIntClr

Address:

0x808D_001C

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RTIS

TIS

RIS

MIS