5 receive descriptor example, 5 receive descriptor example -24, Figure 9-11. receive descriptor example -24 – Cirrus Logic EP93xx User Manual

Page 326

9-24

DS785UM1

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

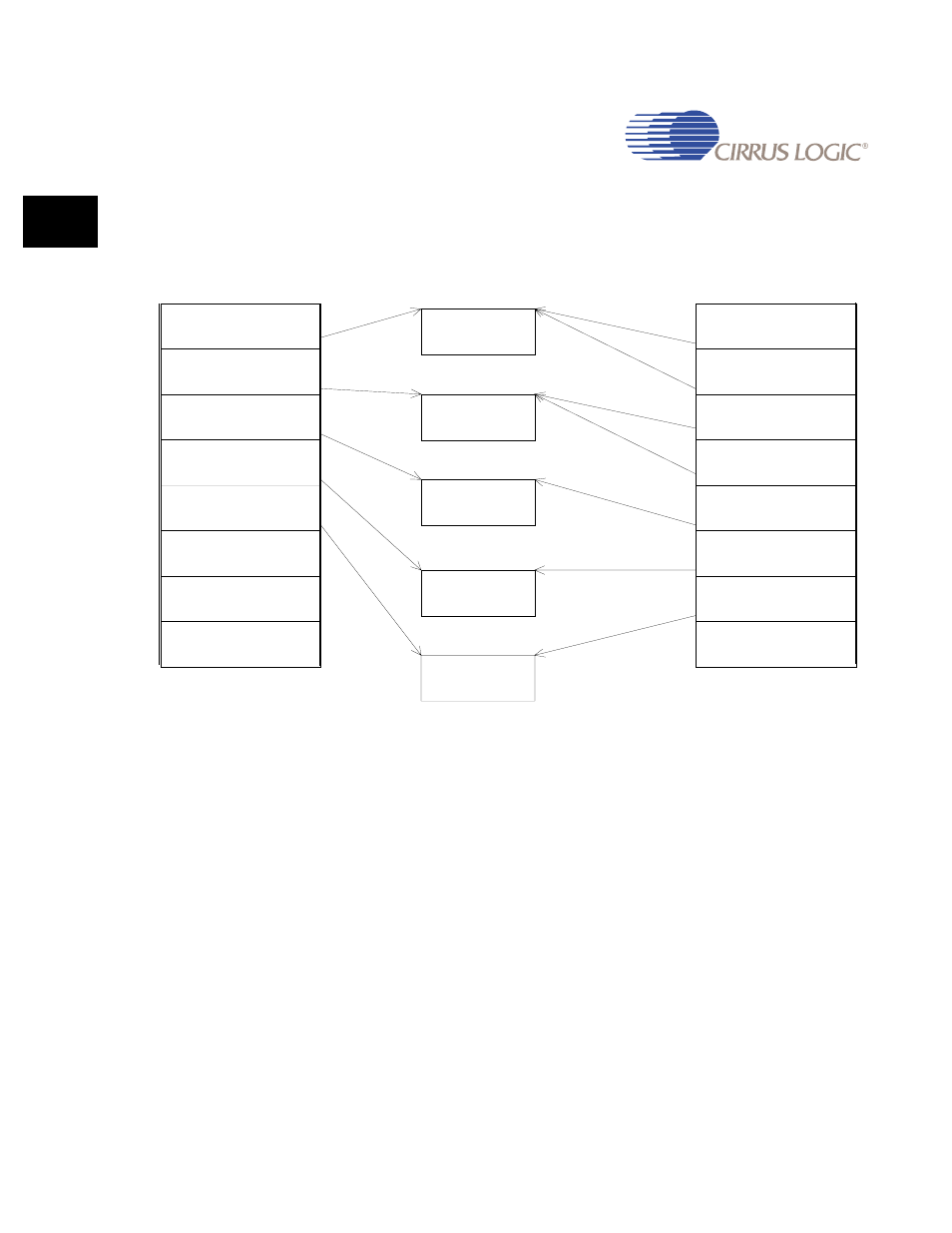

9.2.3.5 Receive Descriptor Example

Figure 9-11. Receive Descriptor Example

shows the state of the receive queues following the reception of four frames. The

first frame uses Data buffer 0 only and there are two status entries associated with it. The first

status (status 0) is for the reception of a receive header and the second (status 1) is for the

end of frame/buffer, both status entries point to the beginning of data buffer 0. The second

frame occupies two buffers (data buffers 1 and 2), and three status entries (2, 3, and 4).

Status 2 is for the receive header, status 3 for the end of buffer 1 (frame size larger than

buffer size), and status 4 for end of frame/buffer. The next two frames both occupy one data

buffer each and one status each. This could be the case for short frames that do not exceed

the header size or the buffer size. The result of this is that the status queue may be used at a

different rate to the descriptor queue, based on the type of traffic and the options selected.

R x D e s crip to r 0

R x D e s crip to r 1

R x D e s crip to r 2

R x D e s crip to r 5

R x D e s crip to r 6

R x D e s crip to r 7

S ta tu s 0

R x H ea d er

S ta tu s 1

E n d o f fra m e &

E n d o f b u ffe r

S ta tus 2

R x H ea d er

Status 3

End of buffer

S ta tu s 4

E n d o f fra m e &

E n d o f b u ffe r

R x D e s crip to r 4

R x D e s crip to r 3

Status 5

End of buffer

S ta tu s 6

E n d o f fra m e &

E n d o f b u ffe r

S tatu s 7

E nd o f fram e &

E nd o f b uffe r

Data buffer 0

Data buffer 1

Data buffer 2

Data buffer 3

Data buffer 4

R e ce ive D e scrip to r

Q u e u e

R e ce ive S ta tu s

Q u e u e