Cirrus Logic EP93xx User Manual

Page 66

2-28

DS785UM1

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

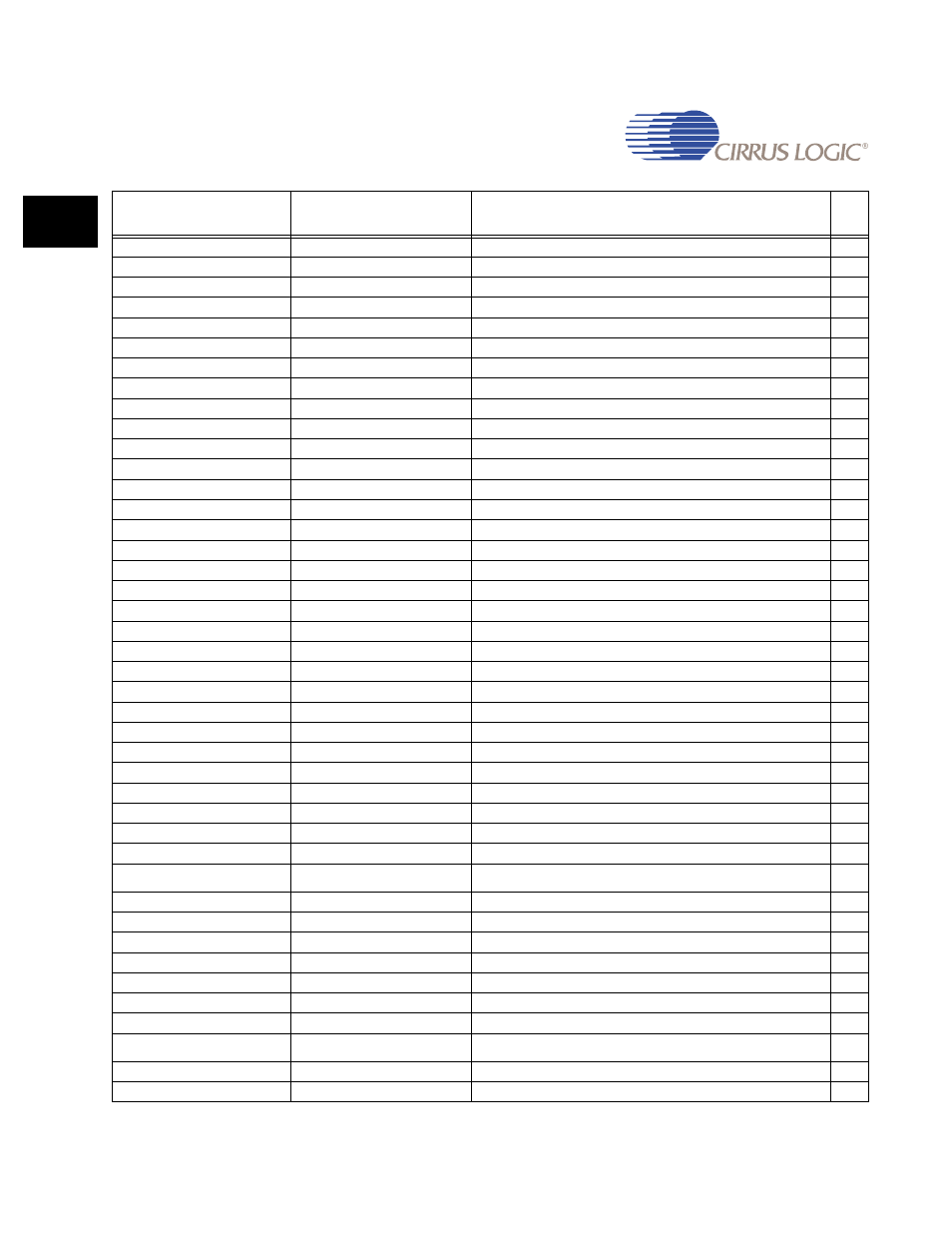

0x8088_0034

AC97ISR2 Interrupt

Status

N

0x8088_0038

AC97IE2 Interrupt

Enable

N

0x8088_003C

Reserved

0x8088_0040

AC97DR3

Data read or written from/to FIFO3

N

0x8088_0044

AC97RXCR3

Control Register for receive

N

0x8088_0048

AC97TXCR3

Control Register for transmit

N

0x8088_004C

AC97SR3

Status Register

N

0x8088_0050

AC97RISR3

Raw interrupt status Register

N

0x8088_0054

AC97ISR3 Interrupt

Status

N

0x8088_0058

AC97IE3 Interrupt

Enable

N

0x8088_005C

Reserved

0x8088_0060

AC97DR4

Data read or written from/to FIFO4

N

0x8088_0064

AC97RXCR4

Control Register for receive

N

0x8088_0068

AC97TXCR4

Control Register for transmit

N

0x8088_006C

AC97SR4

Status Register

N

0x8088_0070

AC97RISR4

Raw interrupt status Register

N

0x8088_0074

AC97ISR4 Interrupt

Status

N

0x8088_0078

AC97IE4 Interrupt

Enable

N

0x8088_007C

Reserved

0x8088_0080

AC97S1Data

Data received/transmitted on SLOT1

N

0x8088_0084

AC97S2Data

Data received/transmitted on SLOT2

N

0x8088_0088

AC97S12Data

Data received/transmitted on SLOT12

N

0x8088_008C

AC97RGIS

Raw Global interrupt status Register

N

0x8088_0090

AC97GIS

Global interrupt status Register

N

0x8088_0094

AC97IM Interrupt

mask

Register

N

0x8088_0098

AC97EOI

End Of Interrupt Register

N

0x8088_009C

AC97GCR Main

Control

Register

N

0x8088_00A0

AC97Reset RESET

control

Register

N

0x8088_00A4

AC97SYNC SYNC

control

Register

N

0x8088_00A8

AC97GCIS

Global channel FIFO interrupt status Register

N

0x808A_xxxx

SPI

SPI Control Registers

0x808A_0000

SSP1CR0

SPI1 Control Register 0

N

0x808A_0004

SSP1CR1

SPI1 Control Register 1

N

0x808A_0008

SSP1DR

SPI1 Data Register

N

0x808A_000C

SSP1SR

SPI1 Status Register

N

0x808A_0010

SSP1CPSR

SPI1 Clock Prescale Register

N

0x808A_0014

SSP1IIR

SPI1 Interrupt/Interrupt Clear Register

N

0x808B_xxxx

IrDA

IrDA Control Registers

0x808B_0000

IrEnable

IrDA Interface Enable

N

0x808B_0004

IrCtrl

IrDA Control Register

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock