Cirrus Logic EP93xx User Manual

Page 58

2-20

DS785UM1

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

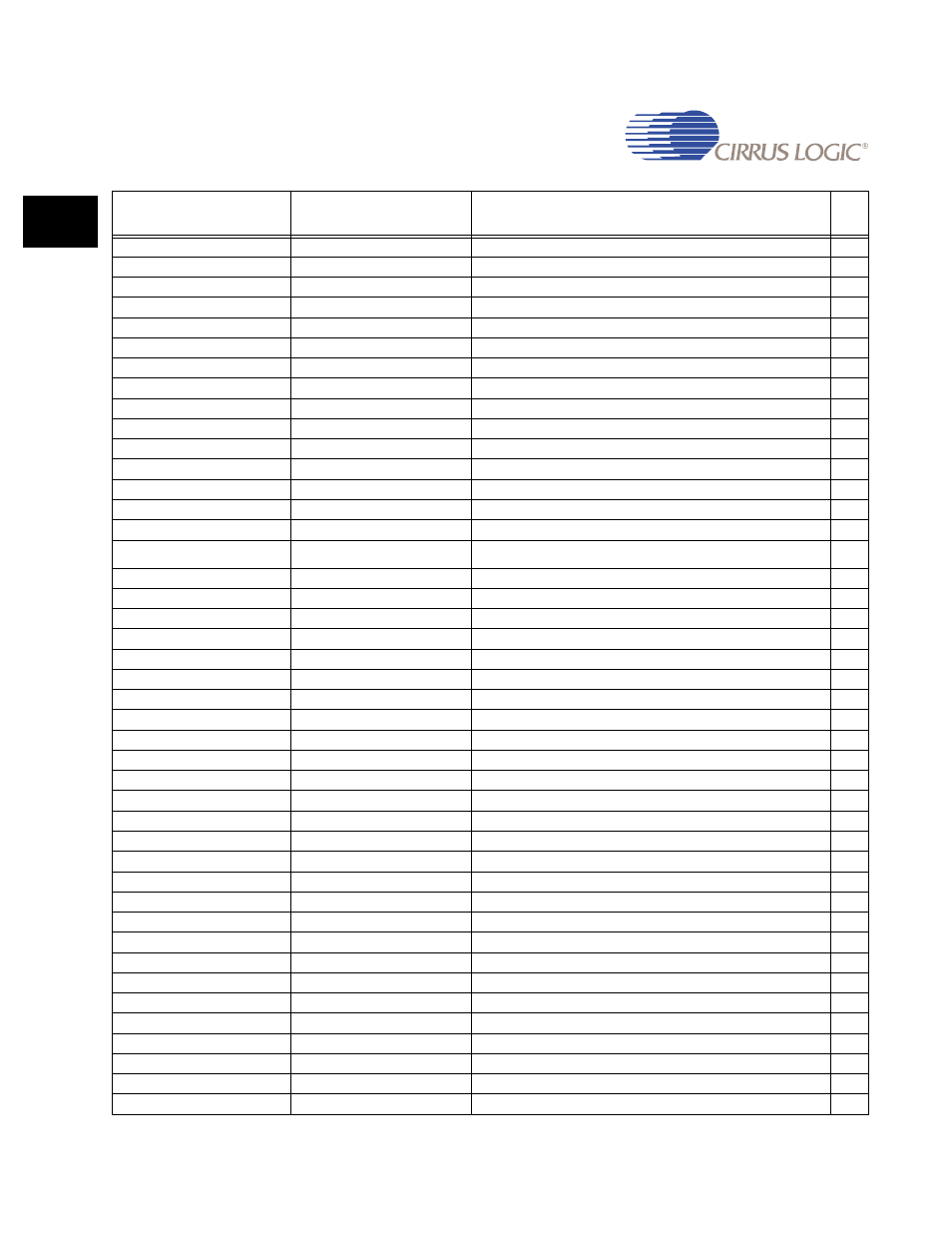

0x8002_0030

HcDoneHead

USB Host Controller Done Head

N

0x8002_0034

HcFmInterval

USB Host Controller Fm Interval

N

0x8002_0038

HcFmRemaining

USB Host Controller Fm Remaining

N

0x8002_003C

HcFmNumber

USB Host Controller Fm Number

N

0x8002_0040

HcPeriodicStart

USB Host Controller Periodic Start

N

0x8002_0044

HcLSThreshold

USB Host Controller LS Threshold

N

0x8002_0048

HcRhDescriptorA

USB Host Controller Root Hub Descriptor A

N

0x8002_004C

HcRhDescriptorB

USB Host Controller Root Hub Descriptor B

N

0x8002_0050

HcRhStatus

USB Host Controller Root Hub Status

N

0x8002_0054

HcRhPortStatus[1]

USB Host Controller Root Hub Port Status 1

N

0x8002_0058

HcRhPortStatus[2]

USB Host Controller Root Hub Port Status 2

N

0x8002_005C

HcRhPortStatus[3]

USB Host Controller Root Hub Port Status 3

N

0x8002_0080

USBCtrl

USB Configuration Control

N

0x8002_0084

USBHCI

USB Host Controller Interface Status

N

0x8003_xxxx

RASTER

Raster Control Registers

0x8003_0000

VLinesTotal

Total Number of vertical frame lines

Y

0x8003_0004

VSyncStrtStop

Vertical sync pulse setup

Y

0x8003_0008

VActiveStrtStop

Vertical blanking setup

Y

0x8003_000C

VClkStrtStop

Vertical clock active frame

Y

0x8003_0010

HClkTotal

Total Number of horizontal line clocks

Y

0x8003_0014

HSyncStrtStop

Horizontal sync pulse setup

Y

0x8003_0018

HActiveStrtStop

Horizontal blanking setup

Y

0x8003_001C

HClkStrtStop

Horizontal clock active frame

Y

0x8003_0020

Brightness

PWM brightness control

N

0x8003_0024

VideoAttribs

Video state machine parameters

Y

0x8003_0028

VidScrnPage

Starting address of video screen

N

0x8003_002C

VidScrnHPage

Starting address of video screen half page

N

0x8003_0030

ScrnLines

Number of active lines scanned to the screen

N

0x8003_0034

LineLength

Length in words of data for lines

N

0x8003_0038

VLineStep

Memory step for each line

N

0x8003_003C

LineCarry

Horizontal/vertical offset parameter

Y

0x8003_0040

BlinkRate

Blink counter setup

N

0x8003_0044

BlinkMask

Logic mask applied to pixel to perform blink operation

N

0x8003_0048

BlinkPattrn

Compare value for determining blinking pixels

N

0x8003_004C

PattrnMask

Mask to limit pattern

N

0x8003_0050

BkgrndOffset

Background color or blink offset value

N

0x8003_0054

PixelMode

Pixel mode definition setup Register

N

0x8003_0058

ParllIfOut

Parallel interface write/control Register

N

0x8003_005C

ParllIfIn

Parallel interface read/setup Register

N

0x8003_0060

CursorAdrStart

Word location of the top left corner of cursor to be displayed

N

0x8003_0064

CursorAdrReset

Location of first word of cursor to be scanned after last line

N

0x8003_0068

CursorSize

Cursor height, width, and step size Register

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock