Cirrus Logic EP93xx User Manual

Page 367

DS785UM1

9-65

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

INT:

Global interrupt force bit, write only, always reads zero.

Writing a one to this bit will set the Global Interrupt Status

bit, if it is enabled. Writing a zero has no effect.

MII/PHY Access Register Descriptions

All PHY registers are accessed through the MII Command, Data and Status Registers. Write

operations are accomplished by writing the required data to the MII Data Register and then

writing the required Command to the MII Command Register (Opcode = 01, PhyAd = target

phy, RegAd = target register), which causes the Busy bit (MII Status) to be set. When the

Busy bit is clear, the write operation has been performed. Read operations are performed by

writing a read command to the MII Command register (Opcode = 10b, PhyAd = target phy,

RegAd = source register), which will also cause the Busy bit (MII Status) to be set. When the

read operation has been completed, the Busy bit is cleared and the read data is available in

the MII Data register.

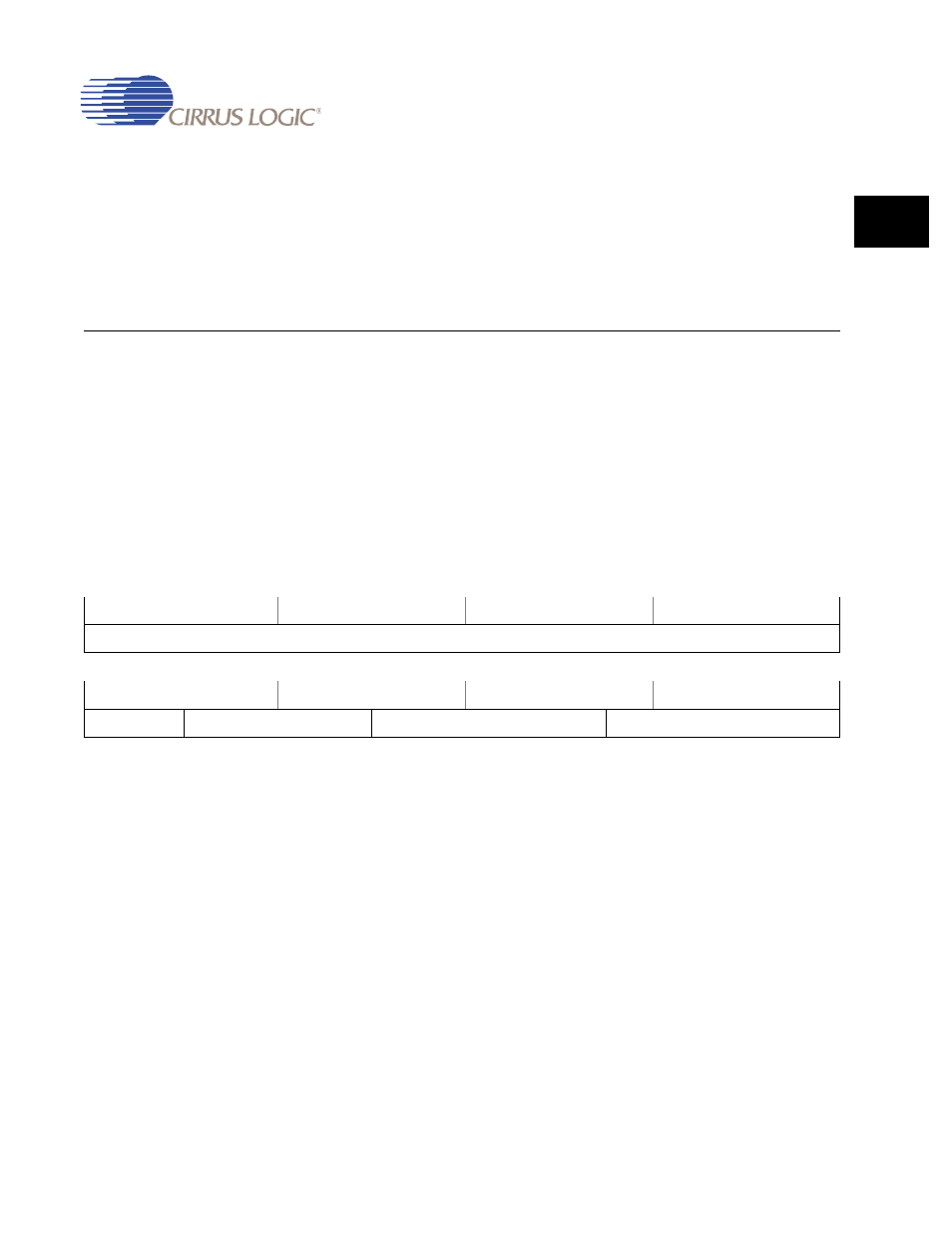

MIICmd

Address:

0x8001_0010 - Read/Write

Chip Reset:

0x0000_0000

Soft Reset:

0x0000_0000

Definition:

MII Command Register. Provides read-write access to the external PHY

registers using the MII command data port.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

OP:

OPcode. This Opcode field defines the type of operation to

be performed to the appropriate PHY register.

10 - Read register

01 - Write register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

OP

RSVD

PHYAD

REGAD