Cirrus Logic EP93xx User Manual

Page 573

DS785UM1

15-15

Copyright 2007 Cirrus Logic

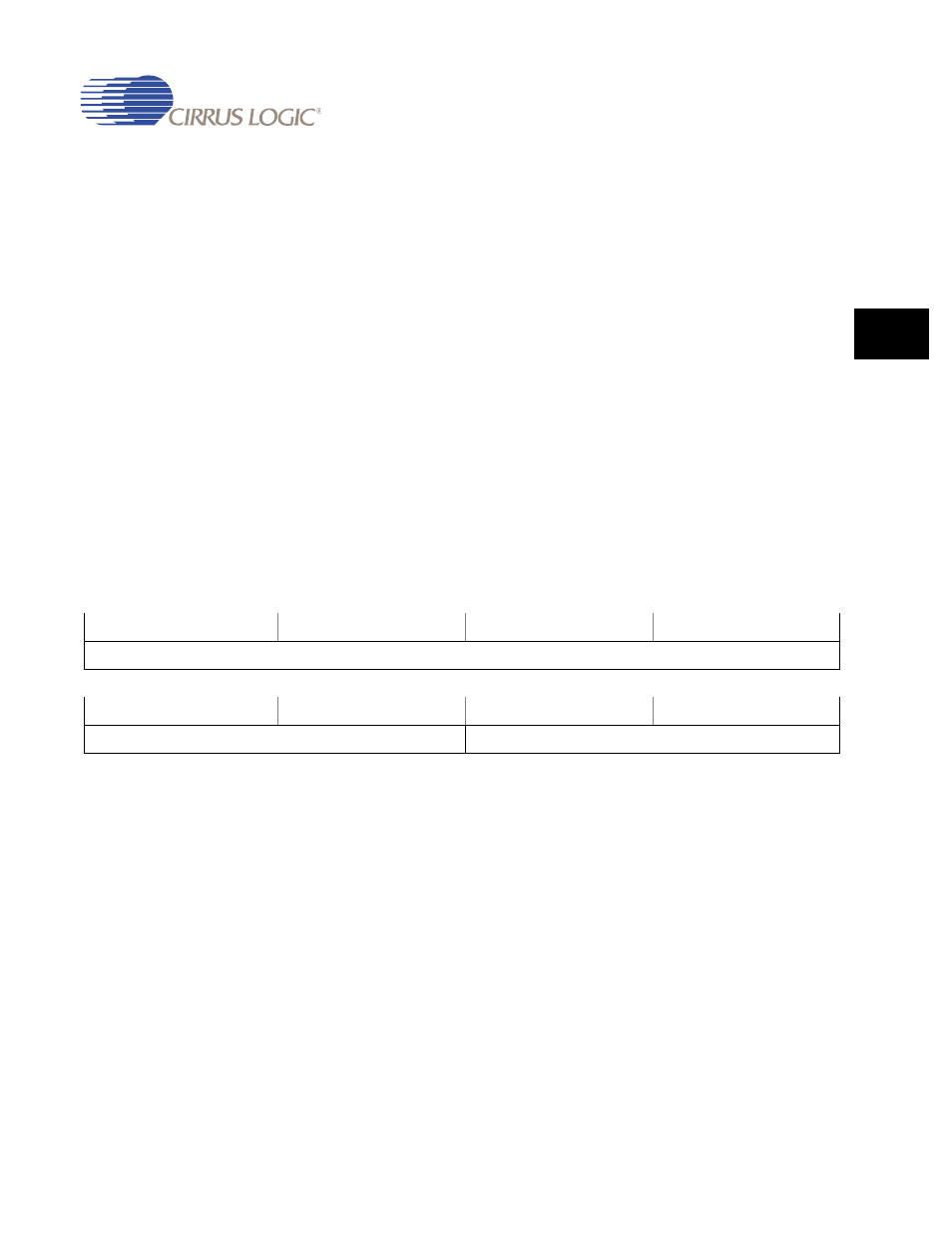

UART2

EP93xx User’s Guide

1

5

1

5

15

Default:

0x0000_0000

Definition:

UART Interrupt Identification and Interrupt Clear Register. Interrupt status is

read from UART2IntIDIntClr. A write to UART2IntIDIntClr clears the modem

status interrupt. All the bits are cleared to 0 when reset.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

RTIS:

Receive Timeout Interrupt Status. This bit is set to “1” if the

receive timeout interrupt is asserted.

TIS:

Transmit Interrupt Status. This bit is set to “1” if the

transmit interrupt is asserted.

RIS:

Receive Interrupt Status. This bit is set to “1” if the receive

interrupt is asserted.

MIS:

Modem Interrupt Status. This bit is set to “1” if the modem

status interrupt is asserted.

UART2IrLowPwrCntr

Address:

0x808D_0020 - Read/Write

Default:

0x0000_0000

Definition:

UART IrDA Low Power Divisor Register. This is an 8-bit read/write register

that stores the low-power counter divisor value used to generate the

IrLPBaud16 signal by dividing down of UARTCLK. All the bits are cleared to 0

when reset.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

ILPDV