Cirrus Logic EP93xx User Manual

Page 627

DS785UM1

17-31

Copyright 2007 Cirrus Logic

IrDA

EP93xx User’s Guide

1

7

1

7

17

DMAERR:

RX DMA error handing enable. If 0, the RX DMA interface

ignores error conditions in the IrDA receive section. If “1”,

the DMA interface stops and notifies the DMA block when

an error occurs. Errors include framing errors, receive

abort, and CRC mismatch.

TXDMAE:

TX DMA interface enable. Setting to “1” enables the

private DMA interface to the transmit FIFO.

RXDMAE:

RX DMA interface enable. Setting to “1” enables the

private DMA interface to the receive FIFO.

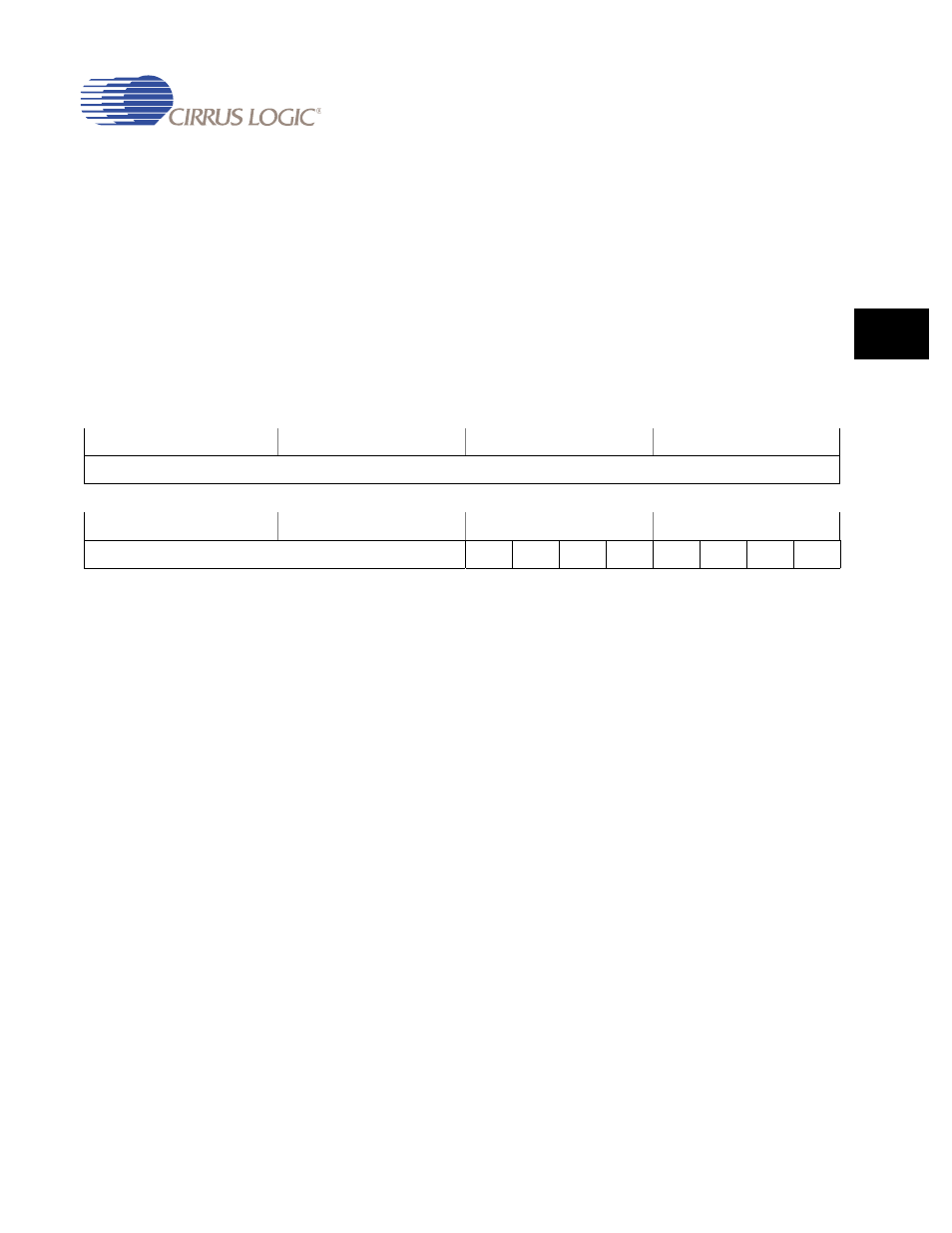

SIRTR0

Address:

0x808B_0030 - Read/Write

Default:

0x0000_0000, except that bit 4 is unknown at reset

Definition:

IrDA Slow InfraRed Test Register 0.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

SIREN:

The state of the SIREN after synchronization. Read only.

SIROUT:

The state of SIROUT output from the InfraRed block. Read

only.

TXD:

The state of the TXD input to the InfraRed block from

UART2. Read only.

RXD:

The state of the RXD output from the InfraRed block to

UART2. Read only.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

SIREN

SIROUT

TXD

RXD

SIRT

SIRIN

S16CLK

TSIRC