Control register description rxctl – Cirrus Logic EP93xx User Manual

Page 343

DS785UM1

9-41

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

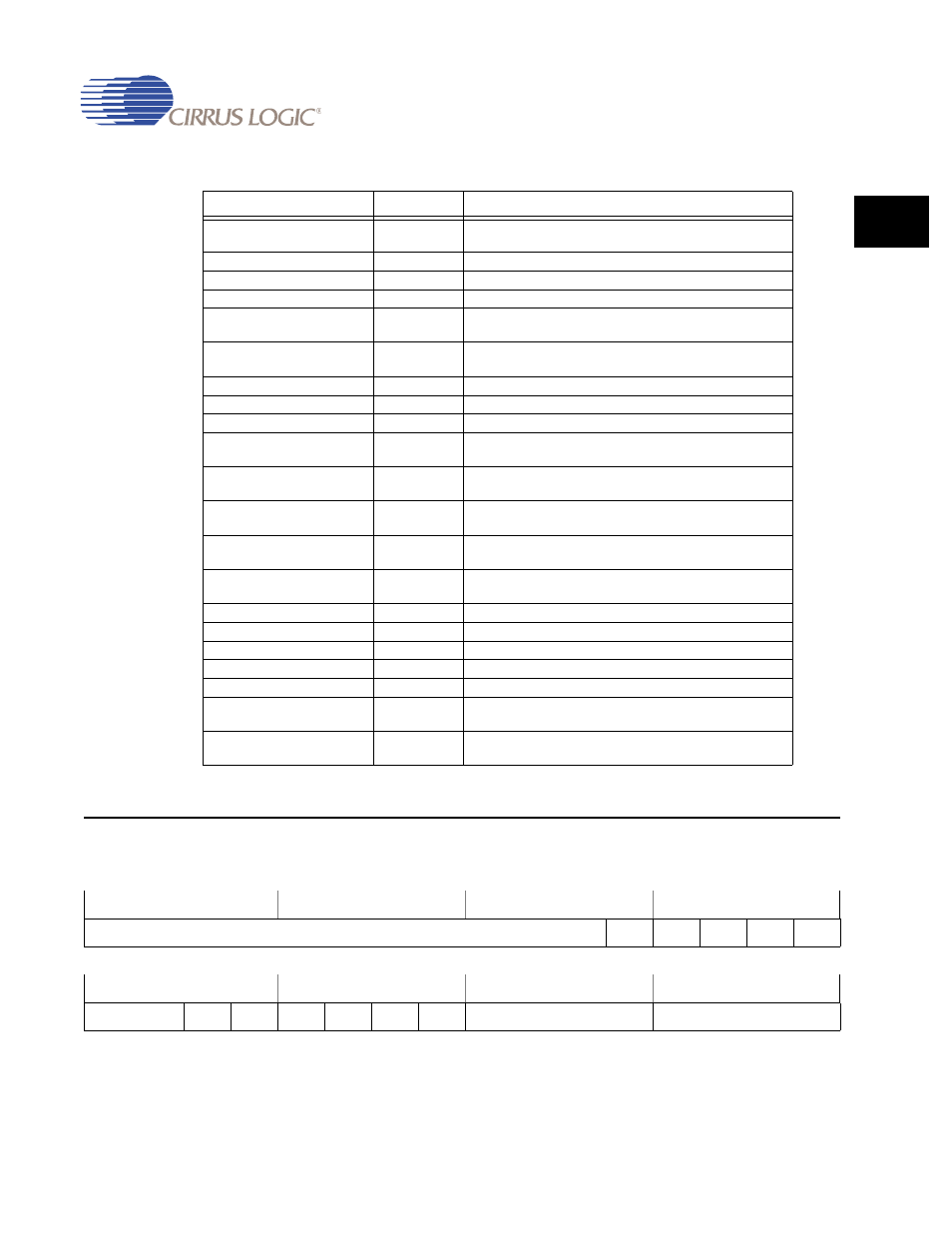

Control Register Description

RXCtl

Address:

0x8001_0000 - Read/Write

0x8001_00A8

RXStsQCurA

dd

MAC Receive Status Queue Current Address Register

0x8001_00AC

RXStsEnq

MAC Receive Status Enqueue Register

0x8001_00B0

TXDQBAdd

MAC Transmit Descriptor Queue Base Address Register

0x8001_00B4

TXDQBLen

MAC Transmit Descriptor Queue Base Length Register

0x8001_00B6

TXDQCurLe

n

MAC Transmit Descriptor Queue Current Length

Register

0x8001_00B8

TXDQCurAd

d

MAC Transmit Descriptor Current Address Register

0x8001_00BC

TXDEnq

MAC Transmit Descriptor Enqueue Register

0x8001_00C0

TXStsQBAdd

MAC Transmit Status Queue Base Address Register

0x8001_00C4

TXStsQBLen

MAC Transmit Status Queue Base Length Register

0x8001_00C6

TXStsQCurL

en

MAC Transmit Status Queue Current Length Register

0x8001_00C8

TXStsQCurA

dd

MAC Transmit Status Queue Current Address Register

0x8001_00D0

RXBufThrshl

d

MAC Receive Buffer Threshold Register

0x8001_00D4

TXBufThrshl

d

MAC Transmit Buffer Threshold Register

0x8001_00D8

RXStsThrshl

d

MAC Receive Status Threshold Register

0x8001_00DC

TXStsThrshld

MAC Transmit Status Threshold Register

0x8001_00E0

RXDThrshld

MAC Receive Descriptor Threshold Register

0x8001_00E4

TXDThrshld

MAC Transmit Descriptor Threshold Register

0x8001_00E8

MaxFrmLen

MAC Maximum Frame Length Register

0x8001_00EC

RXHdrLen

MAC Receive Header Length Register

0x8001_0100 -

0x8001_010C

Reserved

0x8001_4000 -

0x8001_FFFF

MACFIFO

MAC FIFO RAM

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

PauseA

RxFCE1

RxFCE0

BCRC

SRxON

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RCRCA

RA

PA

BA

MA

IAHA

RSVD

IA3

IA2

IA1

IA0

Table 9-3. Ethernet Register List (Continued)

Address

Name

Description