Cirrus Logic EP93xx User Manual

Page 628

17-32

DS785UM1

Copyright 2007 Cirrus Logic

IrDA

EP93xx User’s Guide

1

7

1

7

17

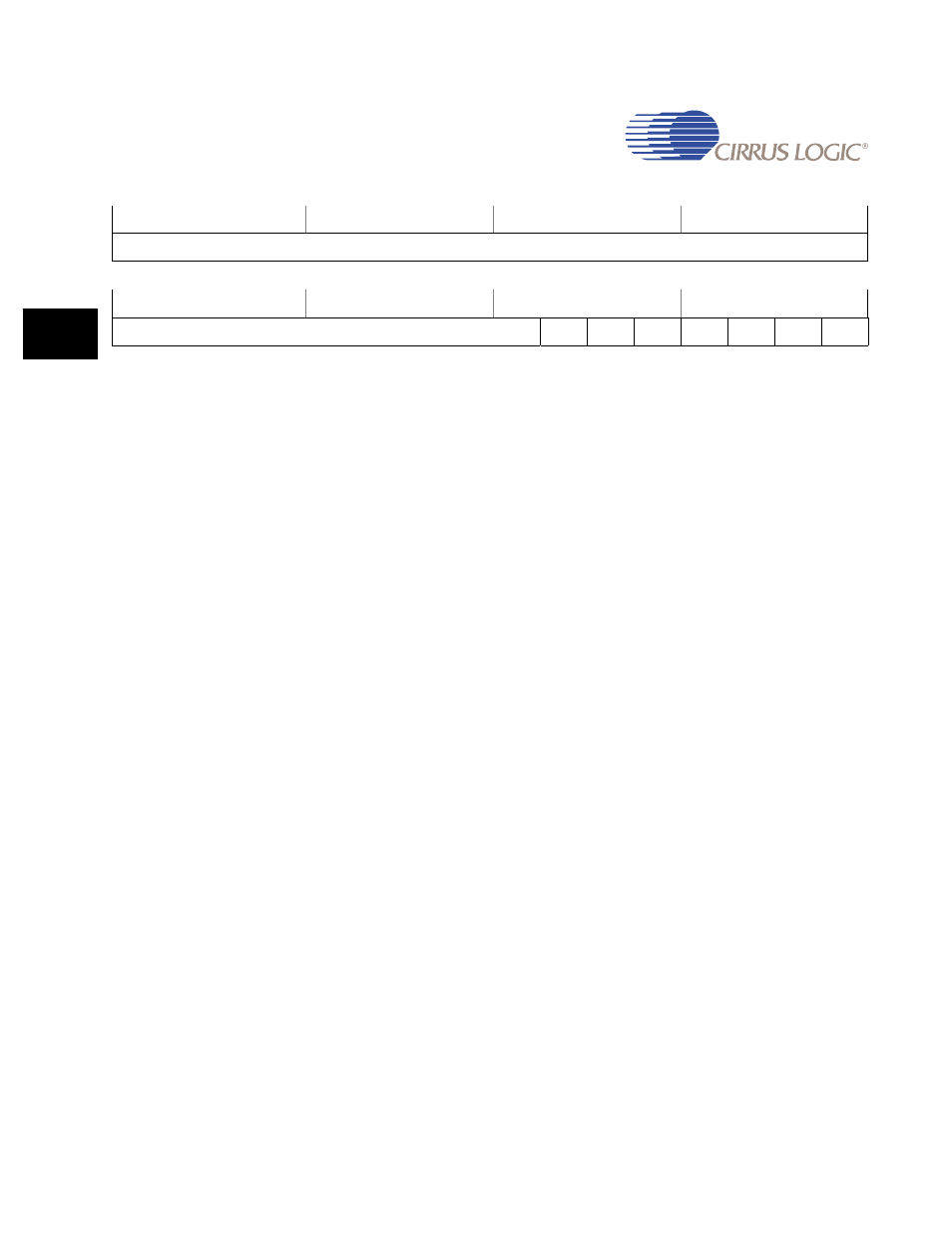

MISR

Address:

0x808B_0080 - Read/Write

Default:

0x0000_0000

Definition:

MIR Status Register.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

RFL:

Receive Frame Lost. Set to a “1” when a ROR occurred at

the start of a new frame, before any data for the frame

could be put into the receive FIFO. This bit is cleared by

writing a “1” to this bit. This occurs if the last entry in the

FIFO already contains a valid EOF bit from a previous

frame when a FIFO overrun occurs. The ROR bit cannot

be placed into the FIFO and all data associated with the

frame is lost.

RIL:

Receive Information Buffer Lost. Set to a “1” when the last

data for a frame is read from the receive FIFO and the

RFC bit is still set from a previous end of frame. This bit is

cleared by writing a “1” to this bit. This is triggered if the

RFC bit is already set before the last data from a frame is

read from the IrData register. It indicates that the data from

the IrRIB register was lost. This can occur if the CPU does

not respond to the RFC interrupt before another (short)

frame completes and is read from the IrData register by

the DMA controller.

RFC:

Received Frame Complete. Set to “1” when the last data

for a frame is read from the receive FIFO (via the IrData

register). This event also triggers the IrRIB to load the

IrFlag and byte count. This bit is cleared when the IrRIB

register is read.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RFL

RIL

RFC

RFS

TAB

TFC

TFS