2 registers, 2 registers -13, Table 5-5. syscon register list -13 – Cirrus Logic EP93xx User Manual

Page 139

DS785UM1

5-13

Copyright 2007 Cirrus Logic

System Controller

EP93xx User’s Guide

5

5

5

5.2 Registers

This section contains the detailed register descriptions for registers in the Syscon block.

shows the address map for the registers in this block, followed by a detailed listing

for each register.

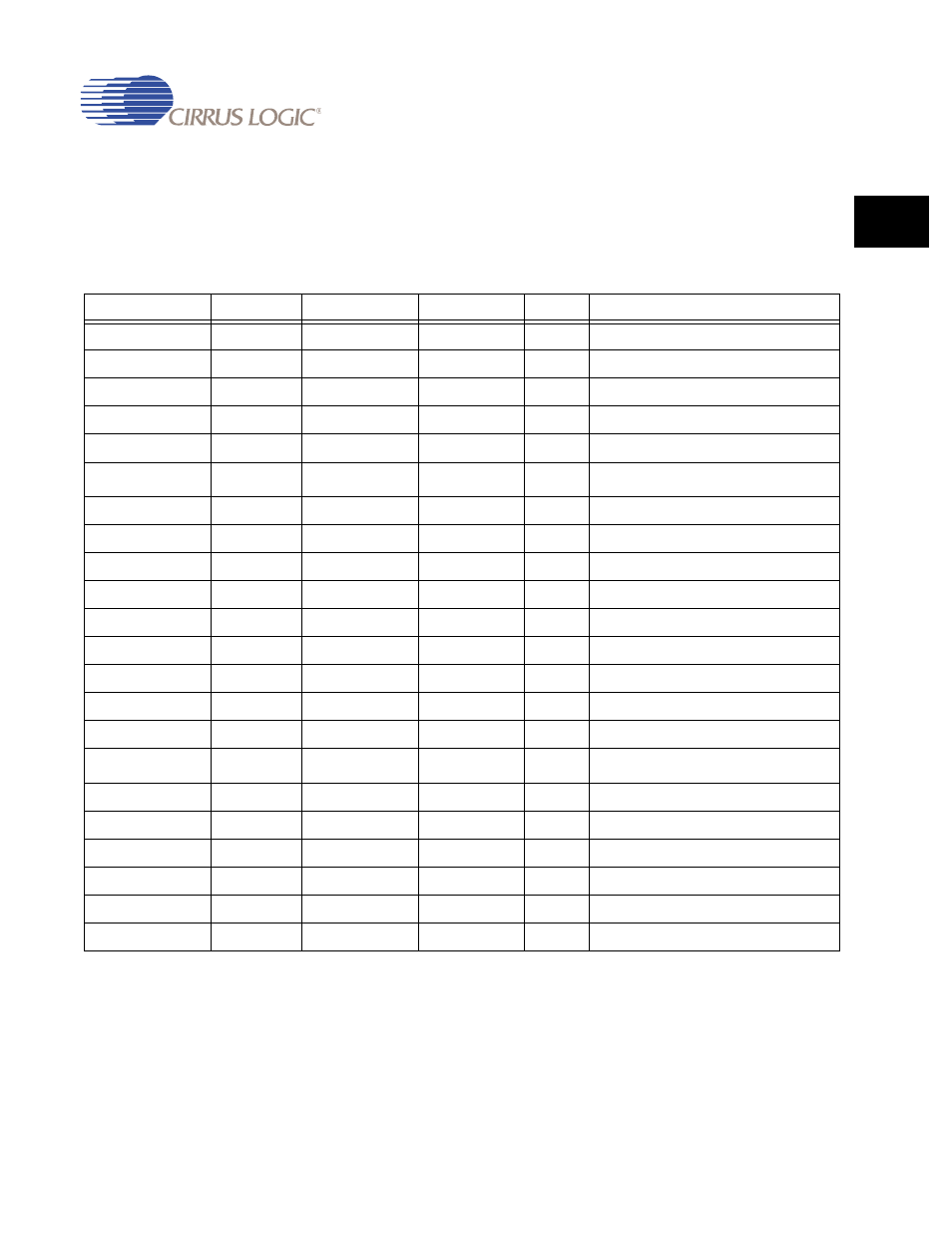

Table 5-5. Syscon Register List

Address

Name

SW Locked

Type

Size

Description

0x8093_0000

PwrSts

No

R

32

Power/state control state

0x8093_0004

PwrCnt

No

R/W

32

Clock/Debug control status

0x8093_0008

Halt

No

R

32

Reading this location enters Halt mode.

0x8093_000C

Standby

No

R

32

Reading this location enters Standby mode.

0x8093_0018

TEOI

No

W

32

Write to clear Tick interrupt

0x8093_001C

STFClr

No

W

32

Write to clear CLDFLG, RSTFLG and

WDTFLG.

0x8093_0020

ClkSet1

No

R/W

32

Clock speed control 1

0x8093_0024

ClkSet2

No

R/W

32

Clock speed control 2

0x8093_0040

ScratchReg0

No

R/W

32

Scratch register 0

0x8093_0044

ScratchReg1

No

R/W

32

Scratch register 1

0x8093_0050

APBWait

No

R/W

32

APB wait

0x8093_0054

BusMstrArb

No

R/W

32

Bus Master Arbitration

0x8093_0058

BootModeClr

No

W

32

Boot Mode Clear register

0x8093_0080

DeviceCfg

Yes

R/W

32

Device configuration

0x8093_0084

VidClkDiv

Yes

R/W

32

Video Clock Divider

0x8093_0088

MIRClkDiv

Yes

R/W

32

MIR Clock Divider, divides MIR clock for

MIR IrDA

0x8093_008C

I2SClkDiv

Yes

R/W

32

I

2

S Audio Clock Divider

0x8093_0090

KeyTchClkDiv

Yes

R/W

32

Keyscan/Touch Clock Divider

0x8093_0094

ChipID

Yes

R/W

32

Chip ID Register

0x8093_009C

SysCfg

Yes

R/W

32

System Configuration

0x8093_00A0

-

-

-

-

Reserved

0x8093_00C0

SysSWLock

No

R/W

1 bit

Software Lock Register