Cirrus Logic EP93xx User Manual

Page 348

9-46

DS785UM1

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

PB:

Pause Busy: This bit remains set as long as a pause

frame is being transmitted. Only one pause frame may be

sent at any time, therefore the Send Pause and Pause

Busy bits should be zero before a new pause frame is

defined.

STxON:

Serial Transmit ON. The transmitter is enabled when set.

When clear, no transmissions are allowed. When a frame

is being transmitted, and STxON is cleared, then that

transmit frame is completed. No subsequent frames are

transmitted until STxON is set again.

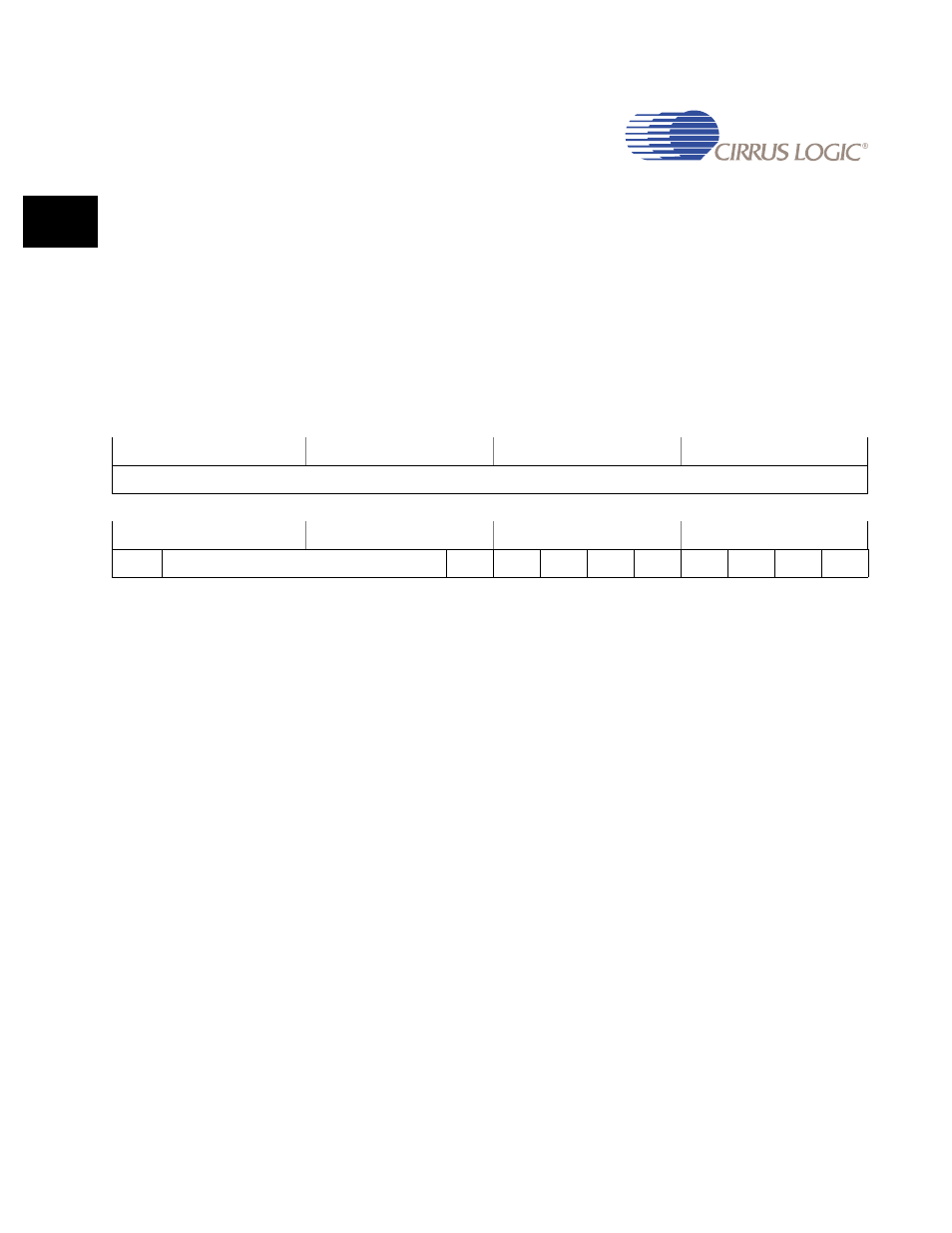

SelfCtl

Address:

0x8001_0020 - Read/Write

Chip Reset:

0x0000_0F10

Soft Reset:

0x0000_0000

Definition:

Self Control Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

MDCDIV:

MDC Clock Divisor. HCLK is divided by MDCDIV + 1 to

create the MDC clock frequency. Default value is 0x07,

which is divide by 8.

Note: Clause 22.2.2.1 in the IEEE-802-3 specification states that the maximum MDC clock rate

is 2.5 MHz. Most PHYs support clock rates faster than 2.5 MHz. So, modify the MDCDIV

value according to the PHYs specification.

PSPRS:

Preamble Suppress. Default is 1.

1 = The first MDC qualifies an SFD on MDIO.

0 = Get 32 ones before SFD.

Note: The user must check the datasheet of the PHY being used in the design. If the PHY needs

a preamble for reading/writing to/from PHY registers, the PSPRS must be cleared (set to

0).

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

MDCDIV

PSPRS

RWP

RSVD

GPO0

PUWE

PDWE

MIIL

RSVD

RESET