Cirrus Logic EP93xx User Manual

Page 56

2-18

DS785UM1

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

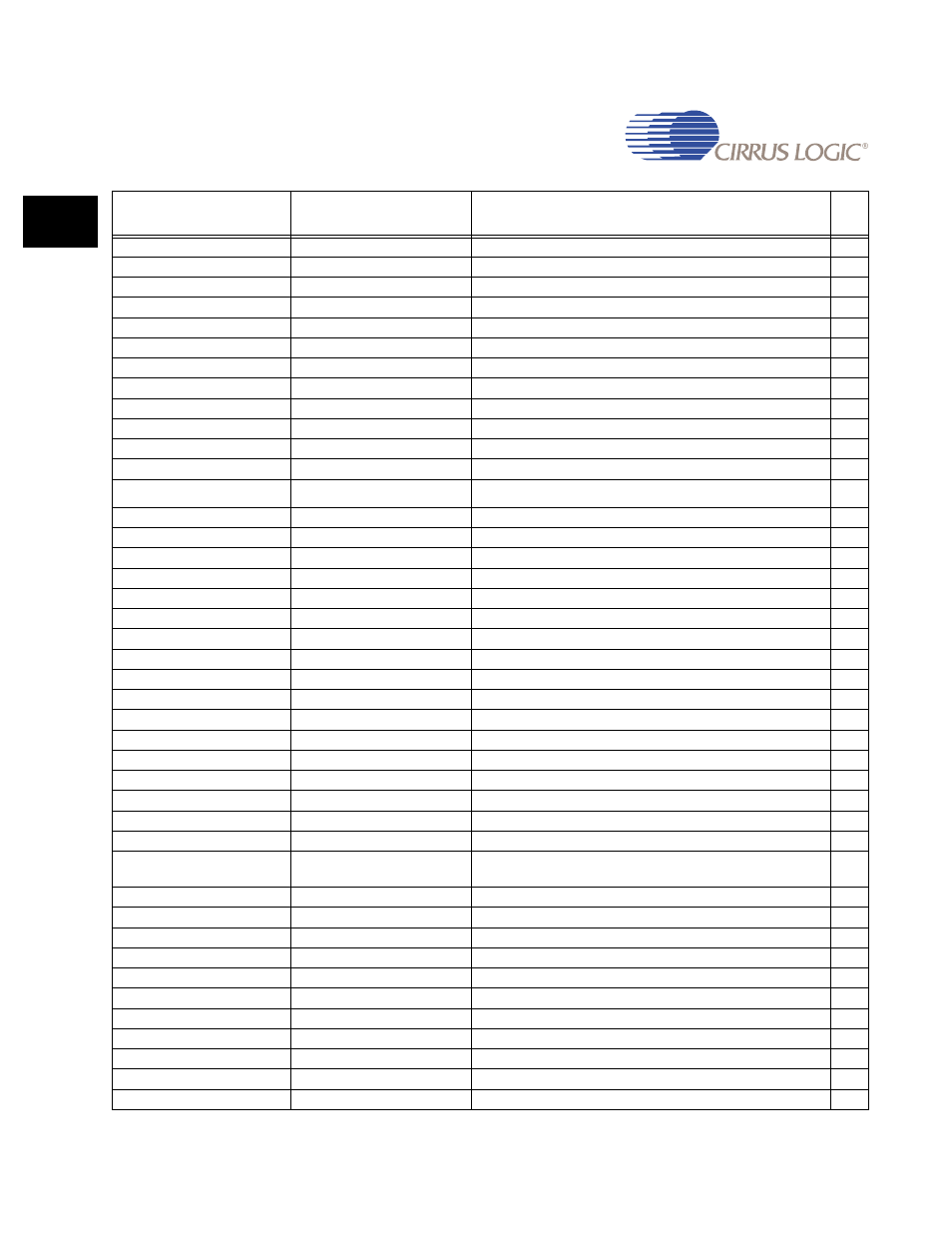

0x8000_0140 - 0x8000_017C

M2M Channel 1 Registers

Memory-to-Memory Channel 1 Registers

N

0x8000_0180 - 0x8000_01FC

Reserved

0x8000_0200 - 0x8000_023C

M2P Channel 5 Registers (Rx)

Memory-to-Peripheral Channel 5 Registers (Rx)

N

0x8000_0240 - 0x8000_027C

M2P Channel 4 Registers (Tx)

Memory-to-Peripheral Channel 4 Registers (Tx)

N

0x8000_0280 - 0x8000_02BC

M2P Channel 7 Registers (Rx)

Memory-to-Peripheral Channel 7 Registers (Rx)

N

0x8000_02C0 - 0x8000_02FC

M2P Channel 6 Registers (Tx)

Memory-to-Peripheral Channel 6 Registers (Tx)

N

0x8000_0300 - 0x8000_033C

M2P Channel 9 Registers (Rx)

Memory-to-Peripheral Channel 9 Registers (Rx)

N

0x8000_0340 - 0x8000_037C

M2P Channel 8 Registers (Tx)

Memory-to-Peripheral Channel 8 Registers (Tx)

N

0x8000_0380

DMAChArb

DMA Channel Arbitration Register

N

0x8000_03C0

DMAGlInt

DMA Global Interrupt Register

N

0x8000_03C4 - 0x8000_FFFC

Reserved

0x8001_xxxx

Ethernet MAC

Ethernet MAC Control Registers

0x8001_0000

RXCtl

MAC Receiver Control Register

N

0x8001_0004

TXCtl

MAC Transmitter Control Register

N

0x8001_0008

TestCtl

MAC Test Control Register

N

0x8001_0010

MIICmd

MAC MII Command Register

N

0x8001_0014

MIIData

MAC MII Data Register

N

0x8001_0018

MIISts

MAC MII Status Register

N

0x8001_0020

SelfCtl

MAC Self Control Register

N

0x8001_0024

IntEn

MAC Interrupt Enable Register

N

0x8001_0028

IntStsP

MAC Interrupt Status Preserve Register

N

0x8001_002C

IntStsC

MAC Interrupt Status Clear Register

N

0x8001_0030 - 0x8001_0034

Reserved

0x8001_0038

DiagAd

MAC Diagnostic Address Register

N

0x8001_003C

DiagDa

MAC Diagnostic Data Register

N

0x8001_0040

GT

MAC General Timer Register

N

0x8001_0044

FCT

MAC Flow Control Timer Register

N

0x8001_0048

FCF

MAC Flow Control Format Register

N

0x8001_004C

AFP

MAC Address Filter Pointer Register

N

0x8001_0050 - 0x8001_0055

IndAd

MAC Individual Address Register, (shares address space with

HashTbl)

N

0x8001_0050 - 0x8001_0057

HashTbl

MAC Hash Table Register, (shares address space with IndAd)

N

0x8001_0060

GlIntSts

MAC Global Interrupt Status Register

N

0x8001_0064

GlIntMsk

MAC Global Interrupt Mask Register

N

0x8001_0068

GlIntROSts

MAC Global Interrupt Read Only Status Register

N

0x8001_006C

GlIntFrc

MAC Global Interrupt Force Register

N

0x8001_0070

TXCollCnt

MAC Transmit Collision Count Register

N

0x8001_0074

RXMissCnt

MAC Receive Miss Count Register

N

0x8001_0078

RXRuntCnt

MAC Receive Runt Count Register

N

0x8001_0080

BMCtl

MAC Bus Master Control Register

N

0x8001_0084

BMSts

MAC Bus Master Status Register

N

0x8001_0088

RXBCA

MAC Receive Buffer Current Address Register

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock