4 sdram initialization, 4 sdram initialization -4, Table 13-3. synchronous memory address decoding -4 – Cirrus Logic EP93xx User Manual

Page 500: Table 13-3

13-4

DS785UM1

Copyright 2007 Cirrus Logic

SDRAM, SyncROM, and SyncFLASH Controller

EP93xx User’s Guide

1

3

1

3

13

the synchronous memory map. Refer to

to compare the memory space with

SROMLL=1 and SROMLL=0. bit can be used to reduce the number of memory segments

and it is

1. “AP” means Auto Precharge -- see SDRAM device’s data sheet

13.4 SDRAM Initialization

Following power on, each SDRAM device must be initialized before it can be used.

shows a general initialization sequence (refer to the SDRAM device’s data sheet to ensure

compatibility).

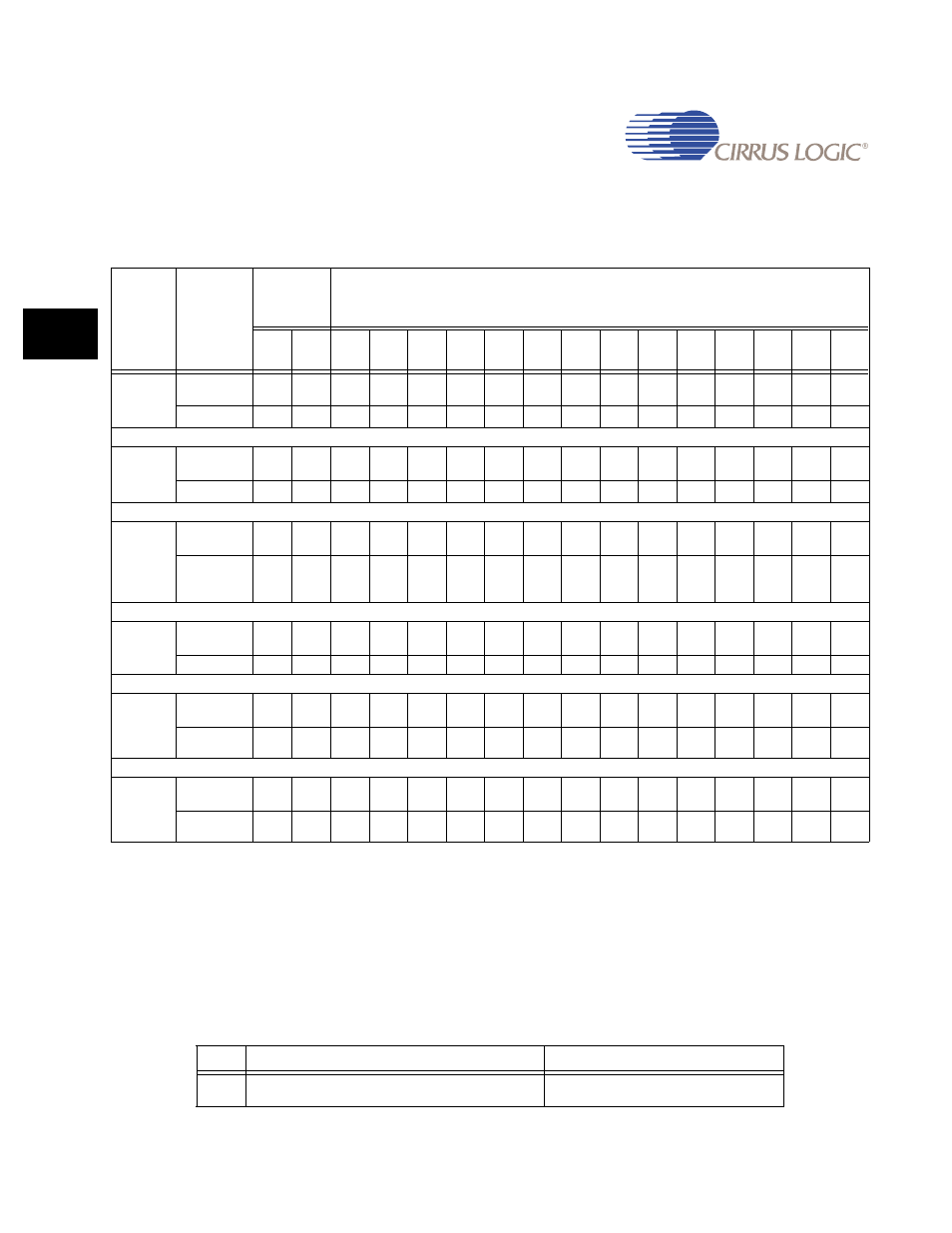

Table 13-3. Synchronous Memory Address Decoding

Sync

Device

Address

Pins

Muxing

Bank

Address

Pins

Address Pins

AD

15

AD

14

AD

13

AD

12

AD

11

AD

10

AD

9

AD

8

AD

7

AD

6

AD

5

AD

4

AD

3

AD

2

AD

1

AD

0

SDRAM

16 bit

data

Row and

Bank

A27

A26

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

Column

A27

A26

-

-

-

AP

1

A25

A24

A8

A7

A6

A5

A4

A3

A2

A1

SDRAM

32 bit

data

Row and

Bank

A27

A26

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

Column

A27

A26

-

-

-

AP

1

A25

A24

A9

A8

A7

A6

A5

A4

A3

A2

SFLASH

2K Page

Mode,

32 bit

data

Row and

Bank

A27

A26

A24

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

Column

A27

A26

-

-

-

AP

1

A25

A10

A9

A8

A7

A6

A5

A4

A3

A2

SROM

512, 32

bit data

Row and

Bank

A27

A26

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

Column

A27

A26

-

-

-

-

A25

A24

A23

A8

A7

A6

A5

A4

A3

A2

SROM

look

alike, 16

bit data

Row and

Bank

A22

A21

A27

A26

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

Column

A22

A21

-

-

-

AP

1

A25

A24

A8

A7

A6

A5

A4

A3

A2

A1

SROM

look

alike, 32

bit data

Row and

Bank

A23

A22

A27

A26

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

Column

A23

A22

-

-

-

AP

1

A25

A24

A9

A8

A7

A6

A5

A4

A3

A2

Table 13-4. General SDRAM Initialization Sequence

Step

Action

Reason

1

Wait 100

μ

s

To allow SDRAM power and clocks to

stabilize