8 gryscllut timing diagram, 8 gryscllut timing diagram -18, Table 7-5. grayscale timing diagram -18 – Cirrus Logic EP93xx User Manual

Page 200

7-18

DS785UM1

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

Where FRAME[1:0] = FRAME_CNT3 or FRAME_CNT4 as defined by FRAME at address

Pixel_In,

VCNT[1:0] = VERT_CNT3 or VERT_CNT4 as defined by VERT at address Pixel_In, and

HCNT[1:0] = HORZ_CNT3 or HORZ_CNT4 as defined by HORZ at address Pixel_In.

This is the GrySclLUT table in an easily readable form. To understand how to use this table

and to know how to fill the table with correct values requires a good understanding on how

the table is used by the grayscale logic.

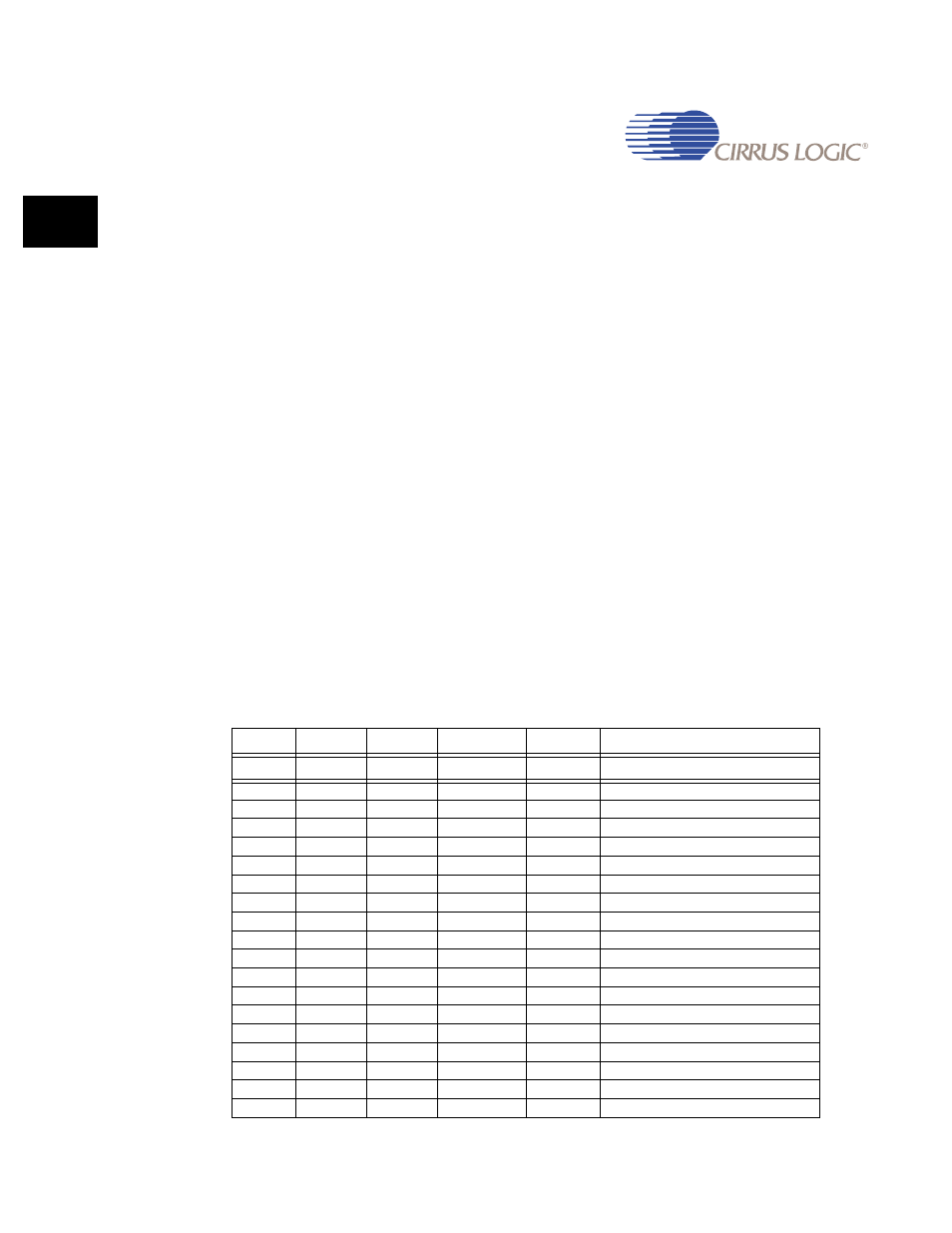

7.4.8.8 GrySclLUT Timing Diagram

shows the timing diagram. The clock column represents a free running master

clock for the display. This clock controls which pixel is being accessed as the image is being

rasterized on the display.

Assume that the first 8 registers have the HCNT, VCNT and FRAME counter registers set up

for 4 counts. The last column shows which register is used to retrieve the look up value and

the bit position within that register that is used as the source to send to the COLORMUX for

the given clock.

Clocks 4, 9, 14, and 19 represent all remaining pixels on the line. Clocks 24 and 29 represent

all remaining pixels for the frame. These entries will keep this example table to a manageable

size.

The FRAME count and PIXEL value are used to indicate which register contains the data.

HCNT and VCNT are used to indicate which bit in the identified register is to be used for the

given grayscale value.

Table 7-5. Grayscale Timing Diagram

Clock

HCNT

VCNT

FRAME

PIXEL

Register Address / Value

Clock

HCNT

VCNT

FRAME

PIXEL

Register Address / Value

0

0

0

0

5

(base + 94) / D0

1

1

0

0

5

(base + 94) / D1

2

2

0

0

5

(base + 94) / D2

3

3

0

0

5

(base + 94) / D3

4

“

“

“

“

5

0

1

0

5

(base + 94) / D4

6

1

1

0

5

(base + 94) / D5

7

2

1

0

5

(base + 94) / D6

8

3

1

0

5

(base + 94) / D7

9

“

“

“

“

10

0

2

0

5

(base + 94) / D8

11

1

2

0

5

(base + 94) / D9

12

2

2

0

5

(base + 94) / D10

13

3

2

0

5

(base + 94) / D11

14

“

“

“

“

15

0

3

0

5

(base + 94) / D12

16

1

3

0

5

(base + 94) / D13

17

2

3

0

5

(base + 94) / D14