5 texas instruments – Cirrus Logic EP93xx User Manual

Page 716

23-4

DS785UM1

Copyright 2007 Cirrus Logic

Synchronous Serial Port

EP93xx User’s Guide

2

3

2

3

23

23.5.5 Texas Instruments

®

Synchronous Serial Frame Format

shows the Texas Instruments synchronous serial frame format for a single

transmitted frame.

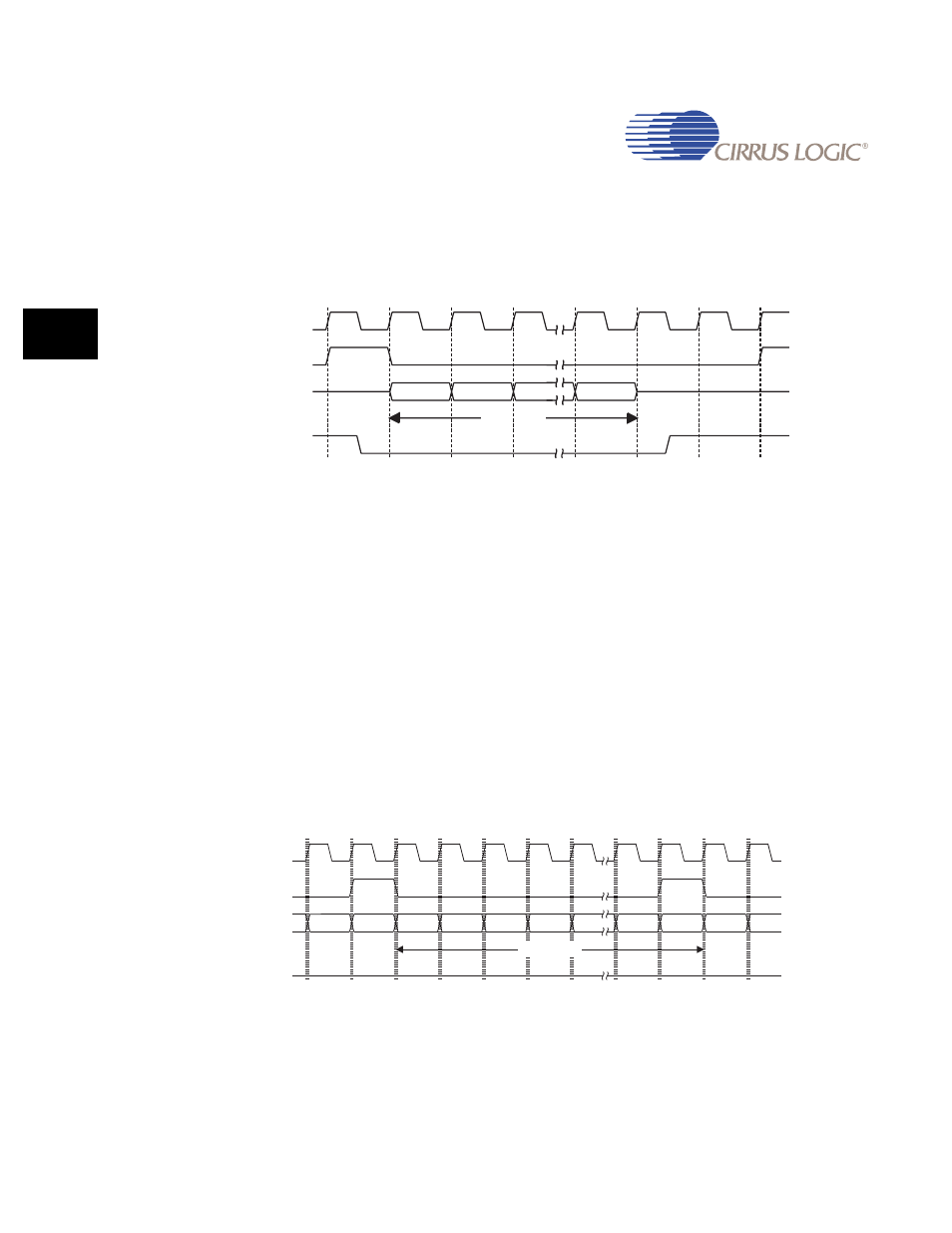

Figure 23-1. Texas Instruments Synchronous Serial Frame Format (Single Transfer)

In this mode, SCLKOUT and SFRMOUT are forced LOW, and the transmit data line SSPTXD

is put in the high impedance state whenever the SSP is idle. Once the bottom entry of the

transmit FIFO contains data, SFRMOUT is pulsed HIGH for one SCLKOUT period. The value

to be transmitted is also transferred from the transmit FIFO to the serial shift register of the

transmit logic. On the next rising edge of SCLKOUT, the MSB of the 4 to 16-bit data frame is

shifted out on the SSPTXD pin. Likewise, the MSB of the received data is shifted onto the

SSPRXD pin by the off-chip serial slave device.

Both the SSP and the off-chip serial slave device then clock each data bit into their serial

shifter on the falling edge of each SCLKOUT. The received data is transferred from the serial

shifter to the receive FIFO on the first rising edge of SCLKOUT after the LSB has been

latched.

shows the Texas Instruments synchronous serial frame format when

back-to-back frames are transmitted.

Figure 23-2. TI Synchronous Serial Frame Format (Continuous Transfer)

4 to 16 bits

M S B

LSB

SSPOE

SSPTXD /

SSPRXD

SFRMOUT /

SFRMIN

SCLKOUT /

SCLKIN

MS B

LSB

4 to 16 bits

SSPOE (=0)

SSPTXD /

SSPRXD

SFRMOUT /

SFRMIN

SCLKOUT /

SCLKIN