Cirrus Logic EP93xx User Manual

Page 708

22-20

DS785UM1

Copyright 2007 Cirrus Logic

AC’97 Controller

EP93xx User’s Guide

2

2

2

2

22

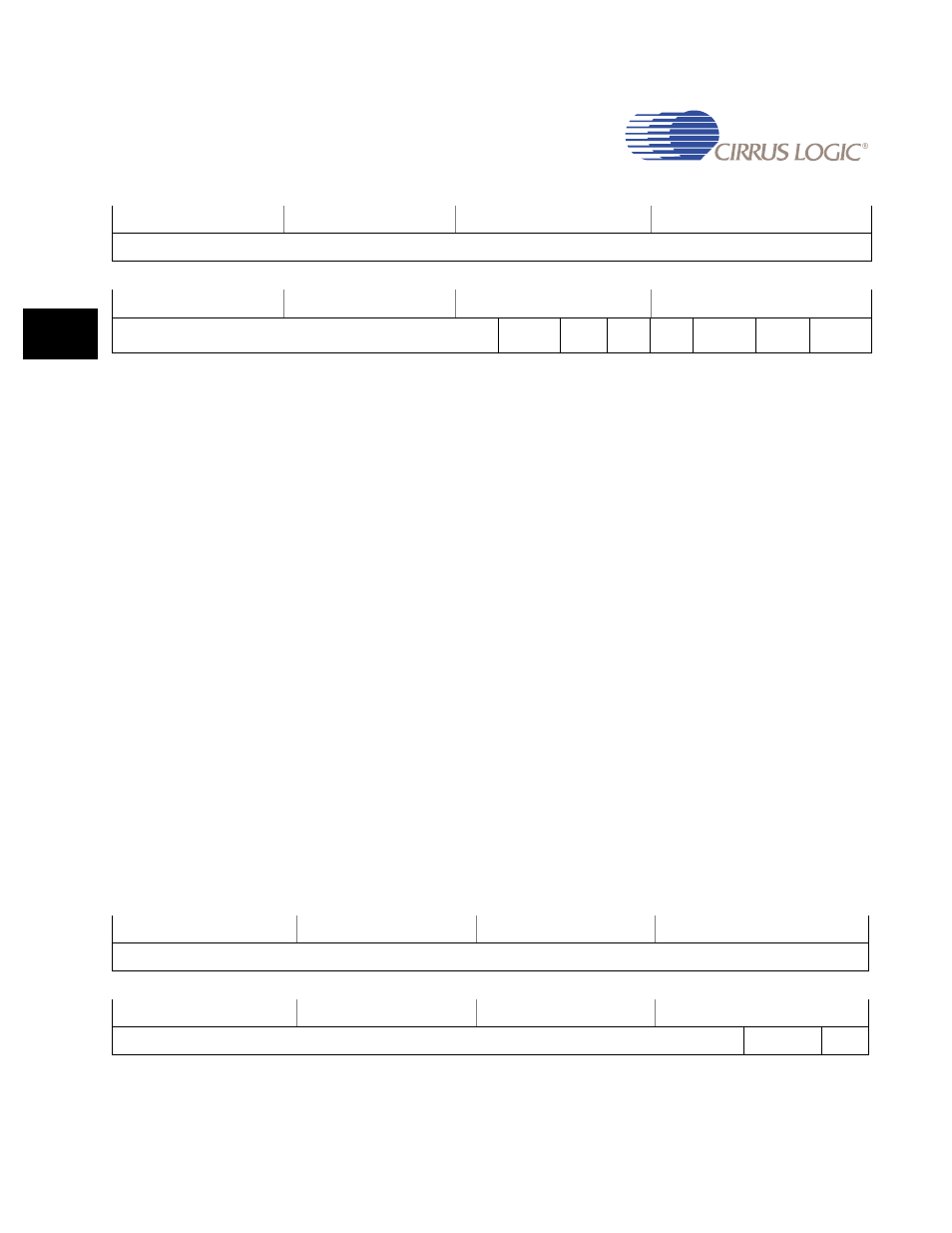

AC97IM

Address:

0x8088_0094 - Read/Write

Definition:

Controller Interrupt Enable Register. The AC’97 Controller interrupt enable

register is a read/write register that controls the interrupt enables for the

interrupts outside the FIFO channels.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

SLOT2TXCOMPLETE:If this bit is set to “1”, the SLOT2TXCOMPLETE

interrupt is enabled.

CODECREADY:

If this bit is set to “1”, the Codec Ready Interrupt is

enabled.

WINT:

If this bit is set to “1”, the Wake-up Interrupt is enabled.

GPIOINT:

If this bit is set to “1”, the GPIO interrupt is enabled.

GPIOTXCOMPLETE:If this bit is set to “1”, the GPIOTXCOMPLETE interrupt

is enabled.

SLOT2RXVALID: If this bit is set to “1”, SLOT2RXVALID interrupt is enabled.

SLOT1TXCOMPLETE:If this bit is set to “1”, SLOT1TXCOMPLETE interrupt is

enabled.

AC97EOI

Address:

0x8088_0098 - Write Only

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

SLOT2TX

COMPLETE

CODEC

READY

WINT

GPIO

INT

GPIOTX

COMPLETE

SLOT2RX

VALID

SLOT1TX

COMPLETE

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

CODECREADY

WINT