Table 3-8. mcr opcode map -17, Table 3-9. mrc opcode map -17, Table 3-8 – Cirrus Logic EP93xx User Manual

Page 87: Table 3-9

DS785UM1

3-17

Copyright 2007 Cirrus Logic

MaverickCrunch Co-Processor

EP93xx User’s Guide

3

3

3

3.5 Instruction Set for the MaverickCrunch Co-Processor

summarizes the MaverickCrunch co-processor instruction set. Please note that:

•

CRd, CRn, and CRm each refer to any of the 16 general purpose MaverickCrunch

registers unless otherwise specified

•

CRa refers to any of the MaverickCrunch accumulators

•

Rd and Rn refer to any of the 16 general purpose ARM920T registers

•

The remainder of this section describes in detail each of the individual MaverickCrunch

instructions. The fields in the opcode for each MaverickCrunch instruction are shown. When

specific bit values are required for the instruction, they are shown as either '1' or '0'. Any field

whose value may vary, such as a register index, is named as in the ARM programming

manuals, and its function described below.

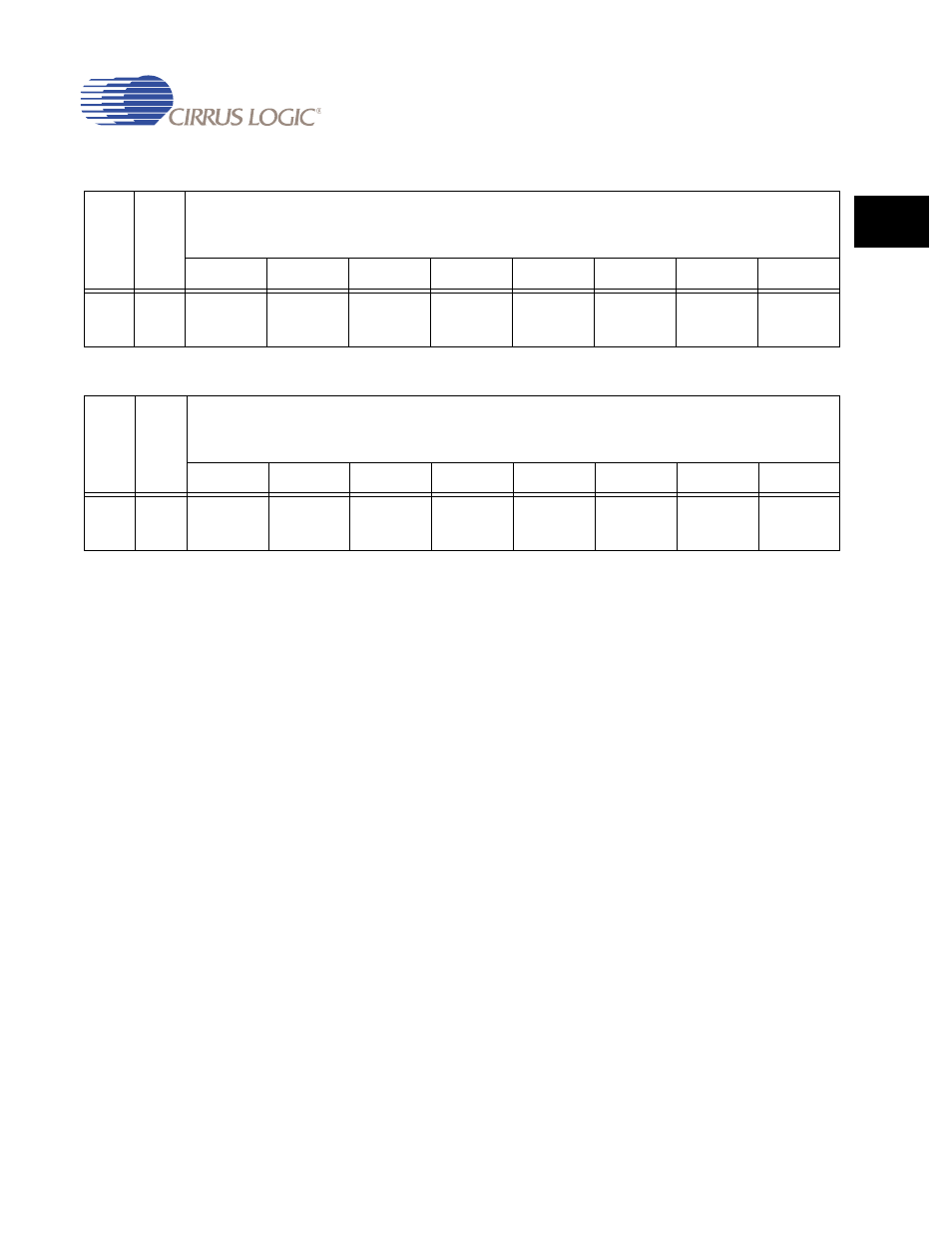

Table 3-8. MCR Opcode Map

op

code1

cp

num

[3:0]

opcode2[2:0]

000

001

010

011

100

101

110

111

0

0100

0101

0110

cfmvdlr

cfmv64lr

cfmvdhr

cfmv64hr

cfmvsr

cfrshl32

cfrshl64

Table 3-9. MRC Opcode Map

op

code1

cp

num

[3:0]

opcode2[2:0]

000

001

010

011

100

101

110

111

0

0100

0101

0110

cfmvrdl

cfmvr64l

cfmvrdh

cfmvr64h

cfmvrs

cfcmps

cfcmp32

cfcmpd

cfcmp64