Lutswctrl – Cirrus Logic EP93xx User Manual

Page 258

7-76

DS785UM1

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

Where:

FRAME[1:0] = FRAME_CNT3 or FRAME_CNT4 as defined by FRAME at address Pixel_In

VCNT[1:0] = VERT_CNT3 or VERT_CNT4 as defined by VERT at address Pixel_In

HCNT[1:0] = HORZ_CNT3 or HORZ_CNT4 as defined by HORZ at address Pixel_In

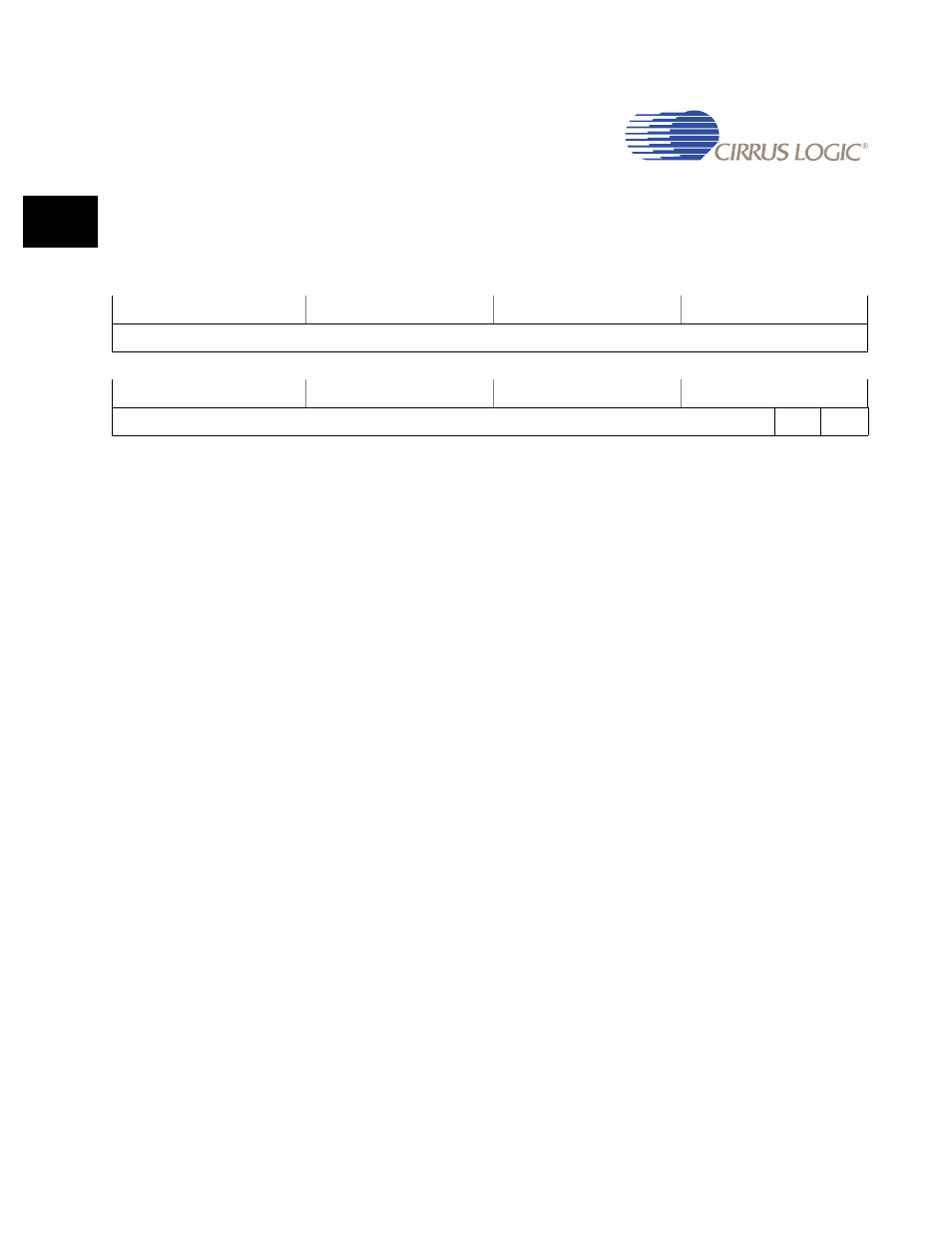

LUTSwCtrl

Address: 0x8003_0218

Default: 0x0000_0000

Definition: LUT Switching Control register

Bit Descriptions:

RSVD:

Reserved - Unknown during read

SSTAT:

Switch Status - Read Only

When SWTCH = ‘0’, Switch Status = ‘1’ means that RAM0

is in the video pipeline and RAM1 is accessible to the bus.

When SWTCH = ‘1’, Switch Status = ‘1’ means that RAM1

is in the video pipeline and RAM0 is accessible to the bus.

During active video, the switch does not occur until the

beginning of the next frame. When the video state

machine is disabled, the switch occurs almost

immediately.

SWTCH:

Switch - Read/Write

Writing a Switch value to this bit selects which of these

conditions is present when SSTAT = ‘1’:

0 - RAM0 in video pipeline, RAM1 is accessible from bus

1 - RAM1 in video pipeline, RAM0 is accessible from bus.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

SSTAT

SWTCH