Cirrus Logic EP93xx User Manual

Page 683

DS785UM1

21-27

Copyright 2007 Cirrus Logic

I

2

S Controller

EP93xx User’s Guide

2

1

2

1

21

i2s_mstr:

Defines if the TX Audio clocks are

slave or master.

0 - slave mode.

1 - master mode.

i2s_trel:

Determines the timing of the lrckt with respect to the sdox

data outputs.

0 - Transition of lrckt occurs together with the first data bit.

1 - Transition of lrckt occurs one bitclk cycle before the first

sdox data bit. This is I

2

S format.

i2s_tckp:

Defines polarity of the TX bitclk.

1 - Positive clock polarity. The lrckt and sdox lines change

synchronously with the positive edge of the bitclk and are

considered valid during negative transitions.

0 - Negative clock polarity. The lrckt and sdox lines change

synchronously with the negative edge of the bitclk and are

considered valid during positive transitions.

i2s_tlrs:

Defines the polarity of lrckt.

0 - if lrckt is low, then it is the left word, if lrckt is high, then

it is the right word.

1 - if lrckt is low, then it is the right word, if lrckt is high,

then it is the left word.

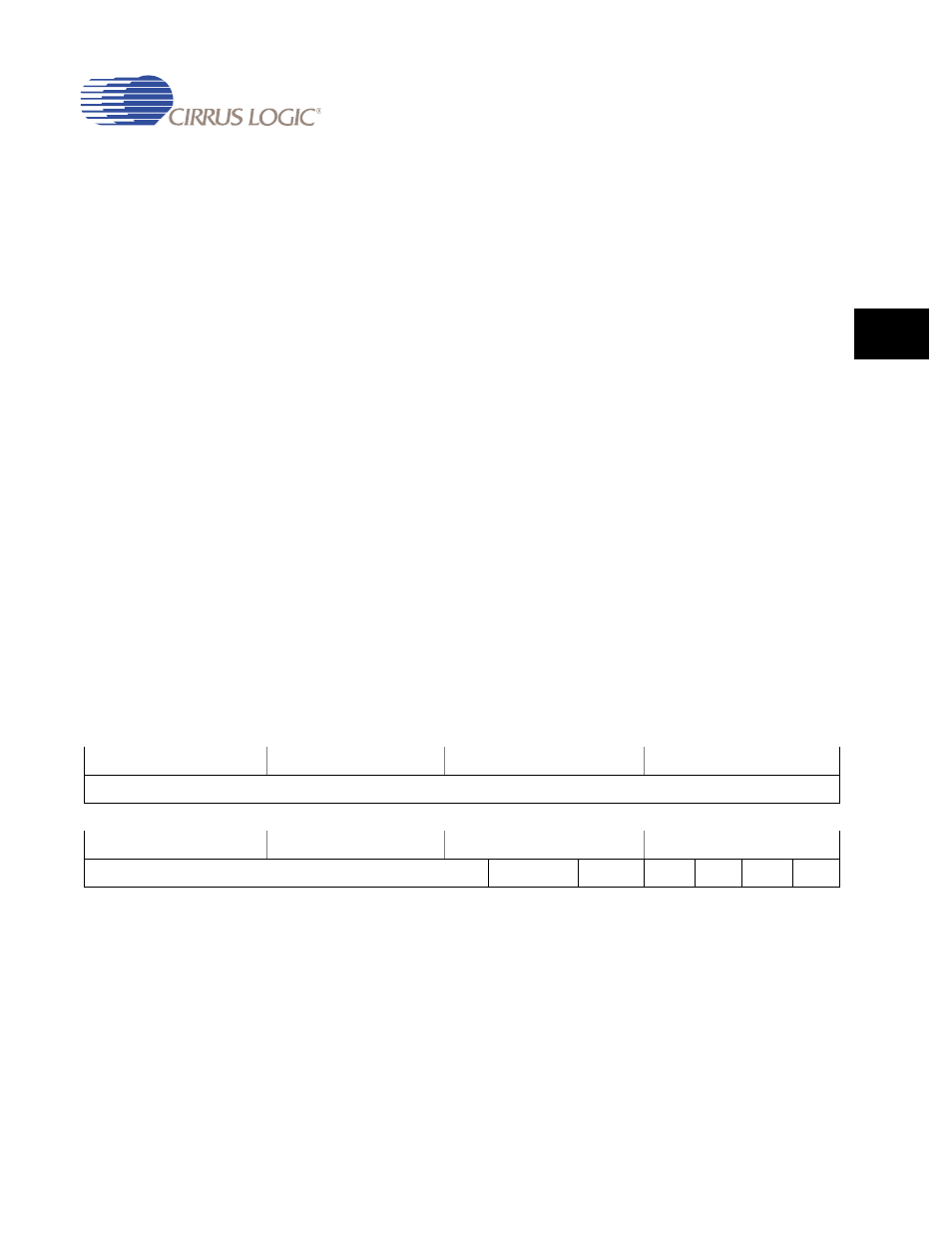

I2SRXClkCfg

Address:

0x8082_0004 - Read/Write

Default:

0x0000_0000

Definition:

Receiver clock configuration register.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

i2s_rx_bcr

i2s_rx_nbcg

i2s_mstr

i2s_rrel

i2s_rckp

i2s_rlrs