2 registers, 2 registers -8, Table 6-2. vicx register summary -8 – Cirrus Logic EP93xx User Manual

Page 170

6-8

DS785UM1

Copyright 2007 Cirrus Logic

Vectored Interrupt Controller

EP93xx User’s Guide

6

6

6

INT_DSP

ARM Core interrupt.

GPIOINTR

Combined Interrupt from Any Bit in Ports A or B. See

,

I2SINTR

Combined Interrupt of All Sources from the I

2

S Controller.

See

,

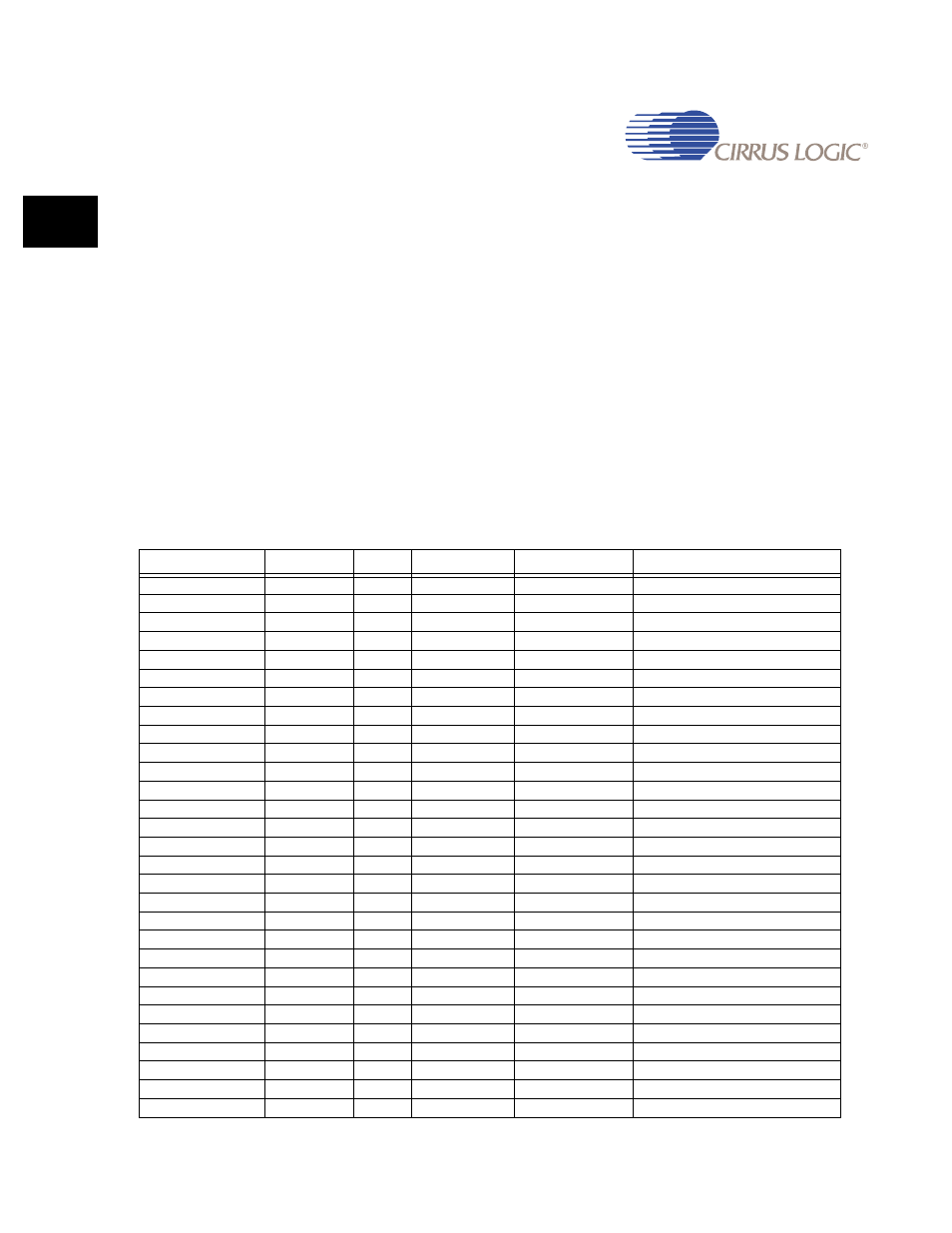

6.2 Registers

The 2 VIC blocks have an identical register definition. The offset from the respective base

address is the same:

•

VIC1 Base address: 0x800B_0000

•

VIC2 Base Address: 0x800C_0000

Using the ARM MMU, it is possible to remap the VIC base address to 0xFFFF_F000, giving a

lower interrupt latency.

indicates the address offset from the base address.

Table 6-2. VICx Register Summary

Address

Type

Width

Reset Value

Name

Description

VIC base + 0000

Read

32

0x0000_0000

IRQ status register

VIC base + 0004

Read

32

0x0000_0000

FIQ status register

VIC base + 0008

Read

32

-

Raw interrupt status register

VIC base + 000C

Read /Write

32

0x0000_0000

Interrupt select register

VIC base + 0010

Read /Write

32

0x0000_0000

Interrupt enable register

VIC base + 0014

Write

32

-

Interrupt enable clear register

VIC base + 0018

Read /Write

32

0x0000_0000

Software interrupt register

VIC base + 001C

Read /Write

32

-

Software interrupt clear register

VIC base + 0020

Read /Write

1

0x0

Protection enable register

VIC base + 0030

Read /Write

32

0x0000_0000

Vector address register

VIC base + 0034

Read /Write

32

0x0000_0000

Default vector address register

VIC base + 0100

Read /Write

32

0x0000_0000

Vector address 0 register

VIC base + 0104

Read /Write

32

0x0000_0000

Vector address 1 register

VIC base + 0108

Read /Write

32

0x0000_0000

Vector address 2 register

VIC base + 010C

Read /Write

32

0x0000_0000

Vector address 3 register

VIC base + 0110

Read /Write

32

0x0000_0000

Vector address 4 register

VIC base + 0114

Read /Write

32

0x0000_0000

Vector address 5 register

VIC base + 0118

Read /Write

32

0x0000_0000

Vector address 6 register

VIC base + 011C

Read /Write

32

0x0000_0000

Vector address 7 register

VIC base + 0120

Read /Write

32

0x0000_0000

Vector address 8 register

VIC base + 0124

Read /Write

32

0x0000_0000

Vector address 9 register

VIC base + 0128

Read /Write

32

0x0000_0000

Vector address 10 register

VIC base + 012C

Read /Write

32

0x0000_0000

Vector address 11 register

VIC base + 0130

Read /Write

32

0x0000_0000

Vector address 12 register

VIC base + 0134

Read /Write

32

0x0000_0000

Vector address 13 register

VIC base + 0138

Read /Write

32

0x0000_0000

Vector address 14 register

VIC base + 013C

Read /Write

32

0x0000_0000

Vector address 15 register

VIC base + 0200

Read /Write

6

0x00

Vector control 0 register

VIC base + 0204

Read /Write

6

0x00

Vector control 1 register