Pcio – Cirrus Logic EP93xx User Manual

Page 493

DS785UM1

12-15

Copyright 2007 Cirrus Logic

Static Memory Controller

EP93xx User’s Guide

1

2

1

2

12

The value written to this field specifies the minimum

‘number of HCLK cycles, minus 1’ that the data strobe,

MCDAENn

,

is asserted during a Read or Write access.

The data strobe assertion time is specified by (AC+1)

HCLK cycles. For example, if AC = 0x10, the data strobe

assertion time is 16 + 1 = 17 cycles of HCLK

HC:

Common space Hold time - Read/Write

The value written to this field specifies the minimum

‘number of HCLK cycles, minus 1’ between de-asserting

the data strobe, MCDAENn

,

and de-asserting the address

strobe, MCADENn.

The Hold time is specified by (HC +1) HCLK cycles. For

example, if HC = 0xC, the Hold time is 12 + 1 = 13 cycles

of HCLK.

PC:

Common space setup time - Read/Write

The value written to this field specifies the ‘number of

HCLK cycles, minus 1’ that the address strobe,

MCADENn, is set up before assertion of the data strobe,

MCDAENn.

The Setup time is specified by (PC+1) HCLK cycles. For

example, if PC = 0x25, the Setup time is 37 + 1 = 38

cycles of HCLK.

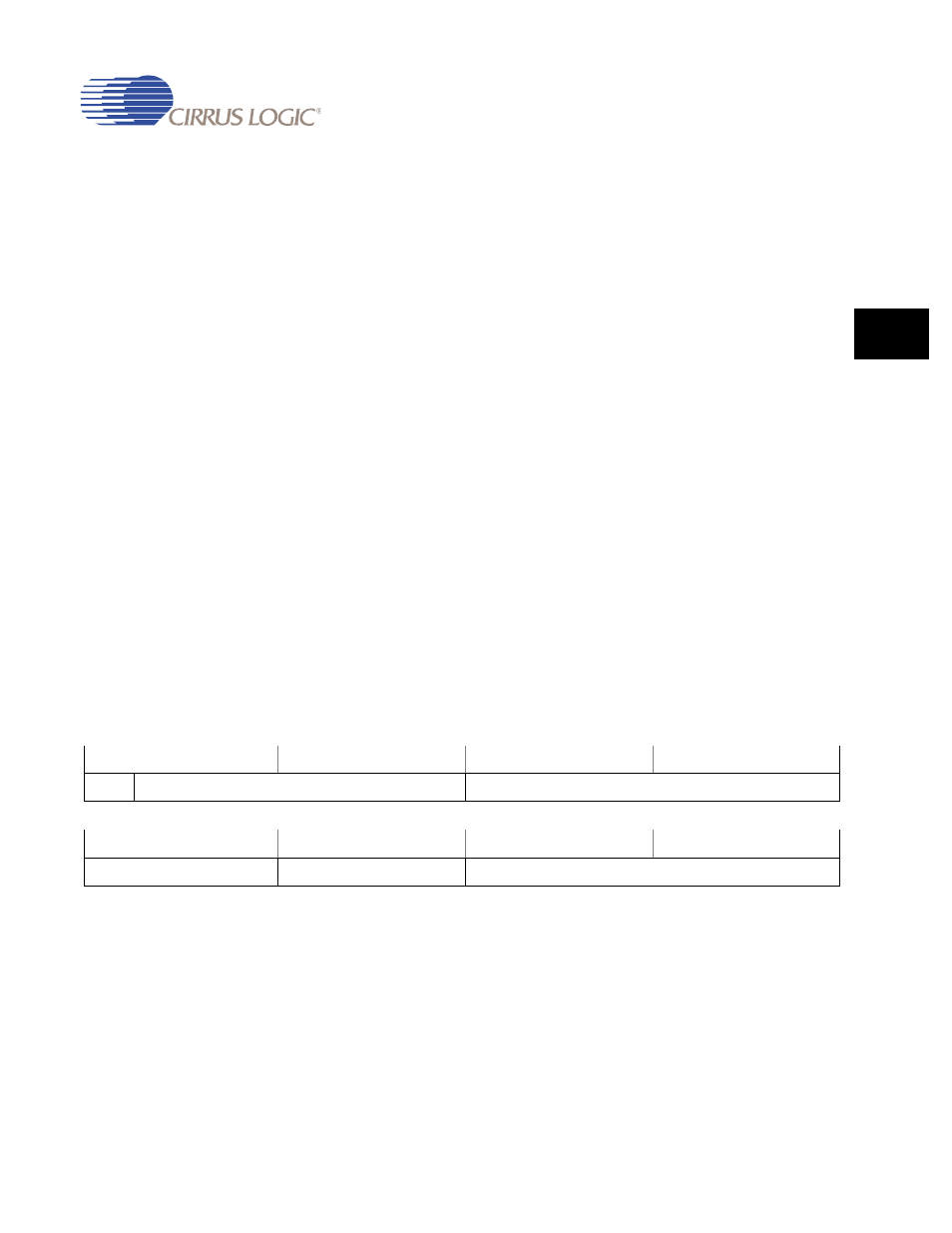

PCIO

Address: 0x8008_0028 - Read/Write

Default: 0x0000_0000

Definition: PC Card IO register

Bit Descriptions:

RSVD:

Reserved - Unknown During Read

WI:

IO Space Width - Read/Write

The value written to this bit specifies the bus-width of the

IO space:

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

WI

RSVD

AI

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

HI

PI