Table 5-6. priority order for ahb arbiter -23, Busmstrarb – Cirrus Logic EP93xx User Manual

Page 149

DS785UM1

5-23

Copyright 2007 Cirrus Logic

System Controller

EP93xx User’s Guide

5

5

5

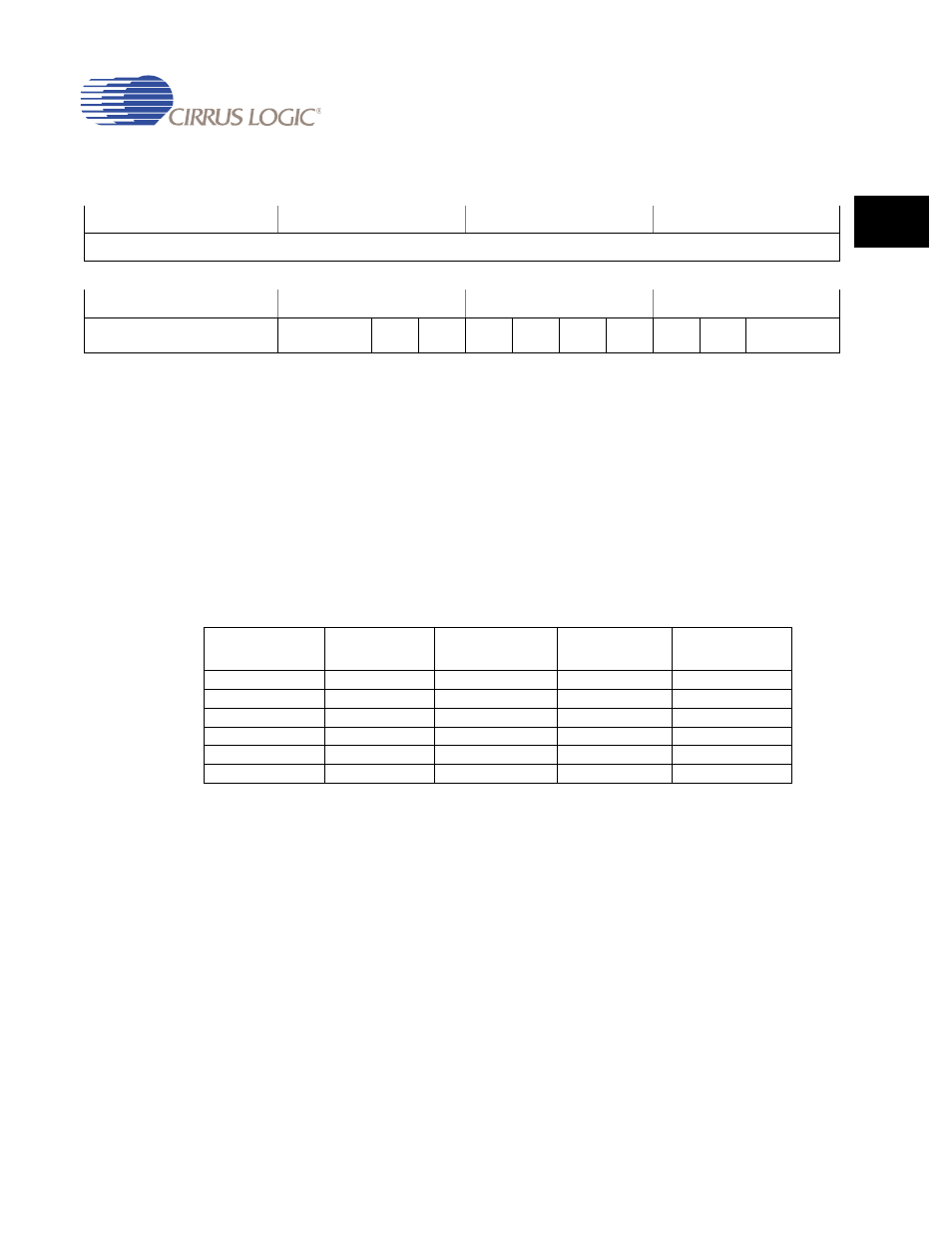

BusMstrArb

Address:

0x8093_0054 - Read/Write

Definition:

The Bus Master arbitration register (BusMstrArb) is used to configure the AHB

master priority order.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

PRI_ORD:

Used to set the priority of the AHB arbiter. The priority

order is shown in

. This field resets to 00.

PRI_CORE:

When this bit is set the Core will become highest priority

following a grant to one of the following: Raster, Raster

Cursor, MAC, USB and DMA. If the Core then requests the

bus, it is then placed in the priority order selected by

PRI_ORD after it is granted, until one of the above

masters is granted the bus, and is placed on top of the

priority scheme.

DMA_ENIRQ:

When set the arbiter will degrant DMA from the AHB bus

and will ignore subsequent requests from DMA if an IRQ is

active. When IRQ is cleared the DMA request is allowed

again. There is no impact on other masters. Reset to 0.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RSVD

MAC

ENFIQ

MAC

ENIRQ

USH

ENFIQ

USH

ENIRQ

DMA_

ENFIQ

DMA_

ENIRQ

PRI

CORE

RSVD

PRI_ORD

Table 5-6. Priority Order for AHB Arbiter

Priority Number

PRIOR 00

(Reset value)

PRIOR 01

PRIOR 10

PRIOR 11

1

Raster Cursor

Raster

Raster

Raster

2

MAC

Raster Cursor

Raster Cursor

DMA

3

USB

MAC

DMA

MAC

4

DMA

USB

USB

USB

5

ARM920T

ARM920T MAC

Raster

Cursor

6

Raster

DMA

ARM920T

ARM920T