7 registers, 7 registers -22, Table 8-22. graphics accelerator registers -22 – Cirrus Logic EP93xx User Manual

Page 286

8-22

DS785UM1

Copyright 2007 Cirrus Logic

Graphics Accelerator

EP93xx User’s Guide

8

8

8

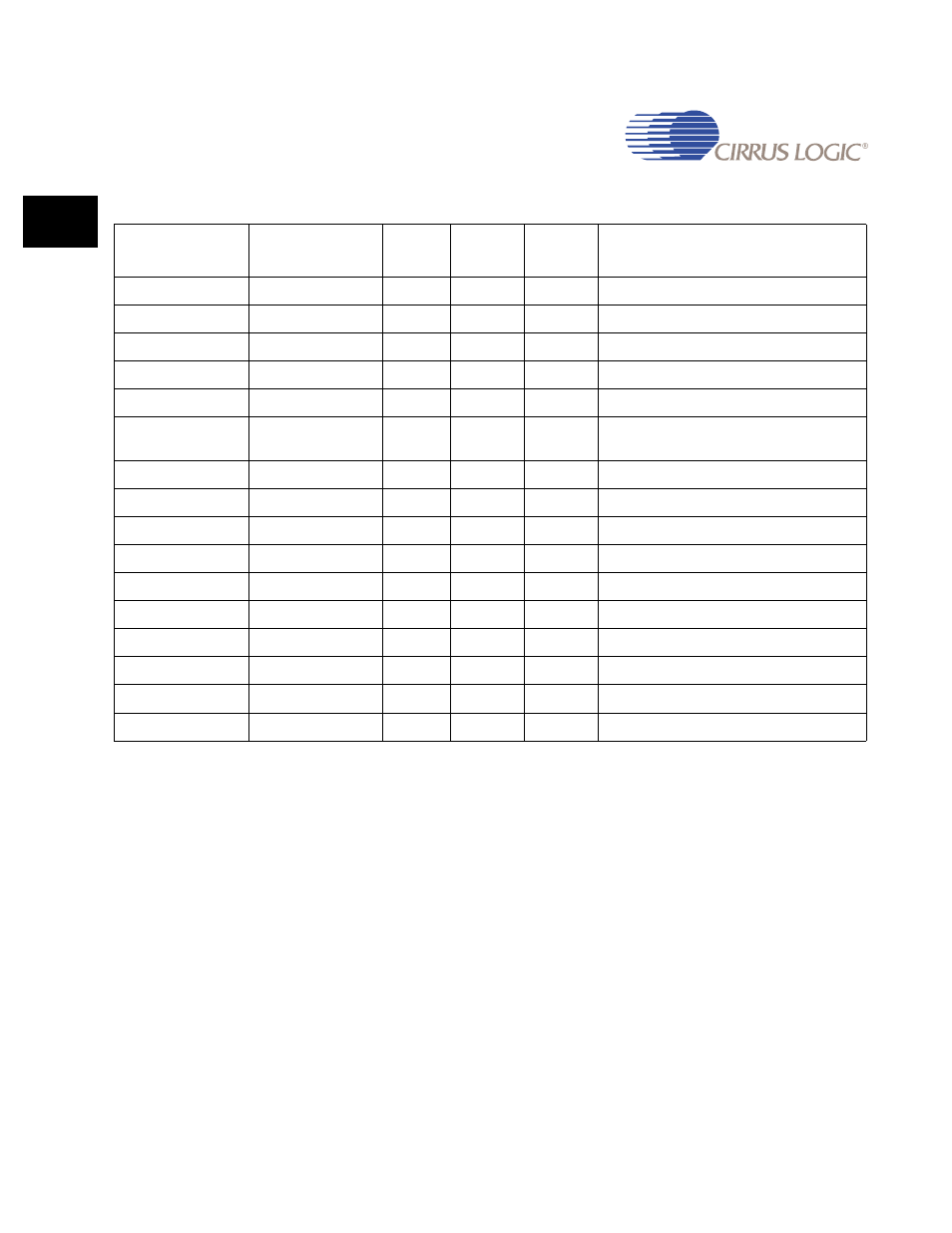

8.7 Registers

Note: Graphics Accelerator registers are intended to be word accessed only. Since the least

significant bytes of the address bus are not decoded, byte and half word accesses are

illegal and may yield unpredictable results.

Table 8-22. Graphics Accelerator Registers

Address

Name

SW

locked

Type

Size

Description

0x8004_0000

No

Read/Write

5 bits

Source Pixel Start Register

0x8004_0004

No

Read/Write

5 + 5 bits

Destination Pixel Start/End Register

0x8004_0008

No

Read/Write

32 bits

Block Source Word Address Start Register

0x8004_000C

No

Read/Write

32 bits

Block Destination Word Address Start Register

0x8004_0010

No

Read/Write

12 bits

Block Function Source Width Register

0x8004_0014

No

Read/Write

12 bits

Block Source Line Length Register

0x8004_0018

No

Read/Write

12 bits

Block Function Destination Width Register

0x8004_001C

No

Read/Write

11 bits

Block Function Destination Height Register

0x8004_0020

No

Read/Write

12 bits

Destination Line Length Register

0x8004_0024

No

Read/Write

16 bits

Block Function Control Register

0x8004_0028

No

Read/Write

24 bits

Block Function Transparency Register

0x8004_002C

No

Read/Write

24 bits

Block Function Mask Register

0x8004_0030

No

Read/Write

24 bits

Block Function Background Register

0x8004_0034

No

Read/Write 12 + 12 bits

Line Draw Increment Register

0x8004_0038

No

Read/Write 12 + 12 bits

Line Draw Initialization Register

0x8004_003C

No

Read/Write

20 bits

Line Pattern Register