Testctl, Inten, Test control register – Cirrus Logic EP93xx User Manual

Page 359

DS785UM1

9-57

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

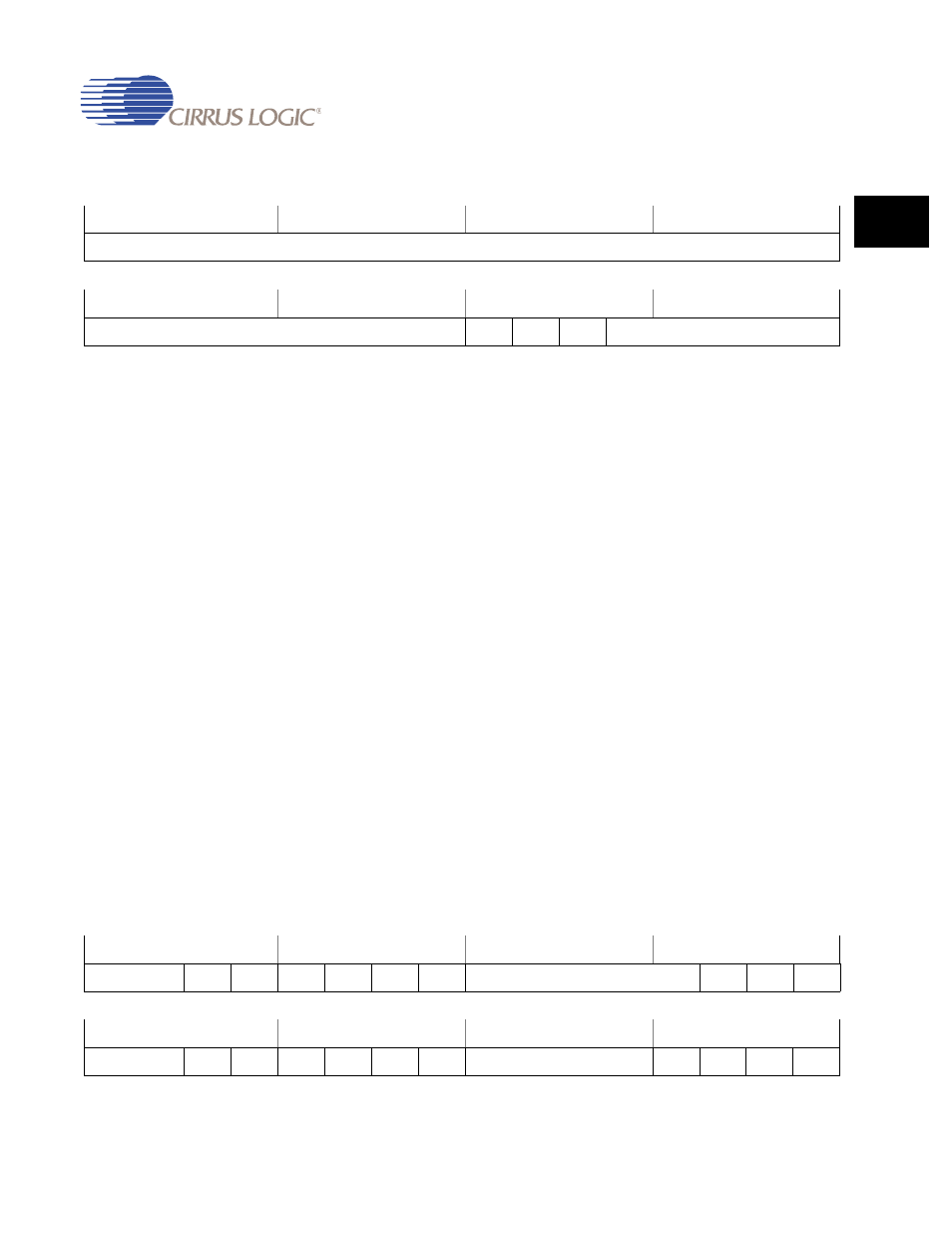

TestCtl

Address:

0x8001_0008 - Read/Write

Chip Reset:

0x0000_0000

Soft Reset:

0x0000_0000

Definition:

Test Control Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

MACF:

MAC Fast. When set, internal MAC timers for link pulses

and collision backoff are scaled in order to speed-up

controller testing. When clear, normal timing is used.

MFDX:

MAC Full Duplex. This bit is used to enable full duplex

operation, when set, the transmitter ignores carrier sense

for transmit deferral. For normal loopback testing this bit

should be set.

DB:

Disable backoff. When set, the backoff algorithm is

disabled. The MAC transmitter looks only for completion of

the Inter Frame Gap before starting transmission. When

clear, the backoff algorithm is used as described in

.

IntEn

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

MACF

MFDX

DB

RSVD

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD / RWIE

RxMIE

RxBIE

RxSQIE

TxLEIE

ECIE

TxUHIE

RSVD

MOIE

TxCOIE

RxROIE

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

RSVD

MIIIE

PHYSIE

TIE

RSVD

SWIE

RSVD

TSQIE

REOFIE

REOBIE

RHDRIE