Cirrus Logic EP93xx User Manual

Page 679

DS785UM1

21-23

Copyright 2007 Cirrus Logic

I

2

S Controller

EP93xx User’s Guide

2

1

2

1

21

RXDIR:

Receive data shift direction.

0 - MSB first

1 - LSB first

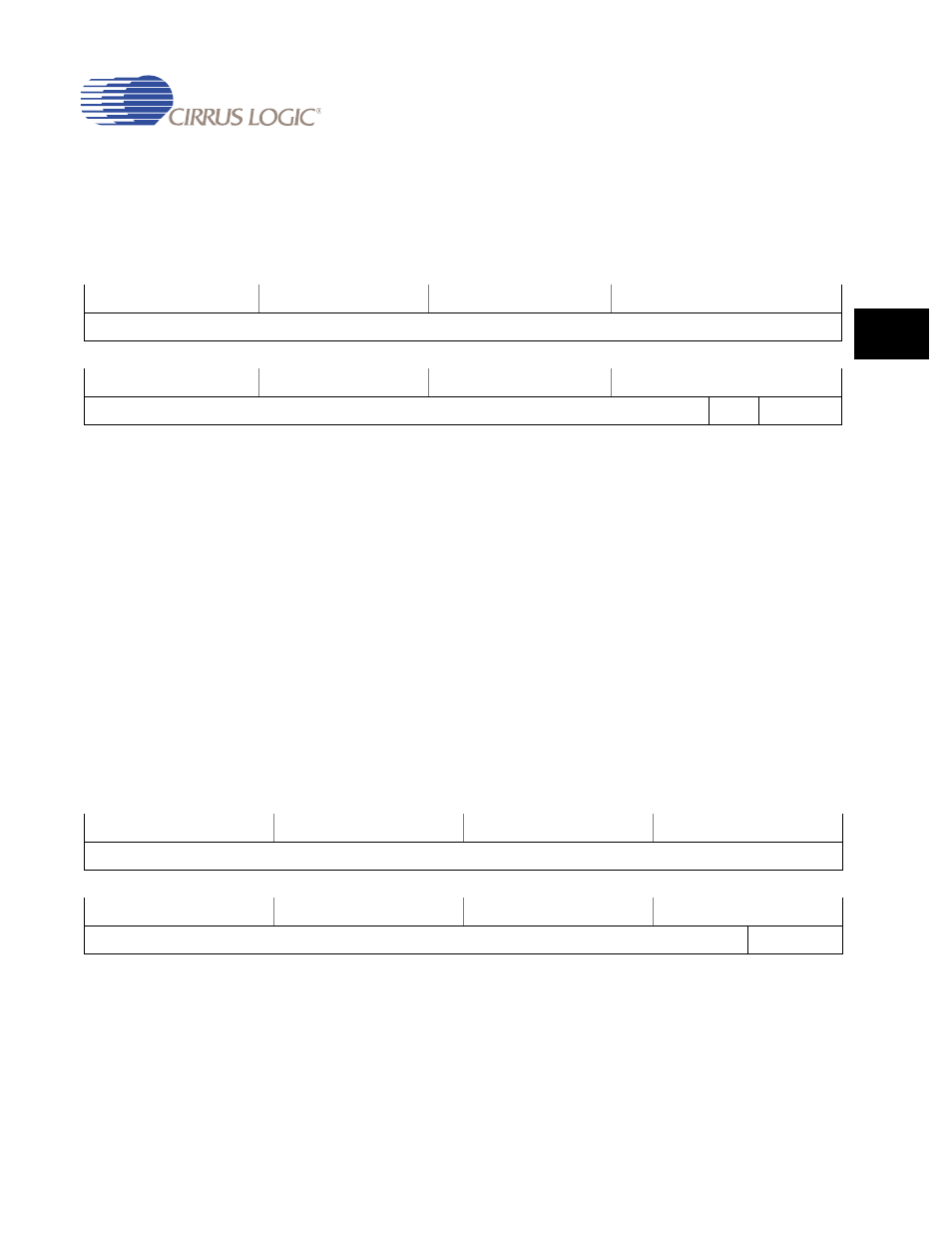

I2SRXCtrl

Address:

0x8082_005C - Read/Write

Default:

0x0000_0000

Definition:

Control Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read. Must be written as “0”.

ROFLIE:

Receive interrupt enable.

Active high

RXFull_int_level:

Rx full interrupt level select.

0 - Generate interrupt when FIFO is half full.

1 - Generate interrupt when FIFO is full.

I2SRXWrdLen

Address:

0x8082_0060 - Read/Write

Default:

0x0000_0000

Definition:

Word Length

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

ROFLIE

RXFull_int_level

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

WL

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1601 (2 pages)

- CS1501 (16 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)