6 interrupt handling, Interrupt, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 59

59

8266A-MCU Wireless-12/09

ATmega128RFA1

Value

Name

Description

5

NO_ACK

No acknowledgement frames were received

during all retry attempts

7

INVALID

Entering TX_ARET mode sets

TRAC_STATUS = 7

Note that if no ACK is expected (according to the content of the received frame in the

Frame Buffer), the radio transceiver issues a TRX24_TX_END interrupt directly after

the frame transmission has been completed. The value of the bits TRAC_STATUS of

register TRX_STATE is set to SUCCESS.

A value of MAX_CSMA_RETRIES = 7 initiates an immediate TX_ARET transaction

without performing CSMA-CA. This is required to support slotted acknowledgement

operation. Further the value MAX_FRAME_RETRIES is ignored and the TX_ARET

transaction is performed only once.

A timing example of a TX_ARET transaction is shown in

.

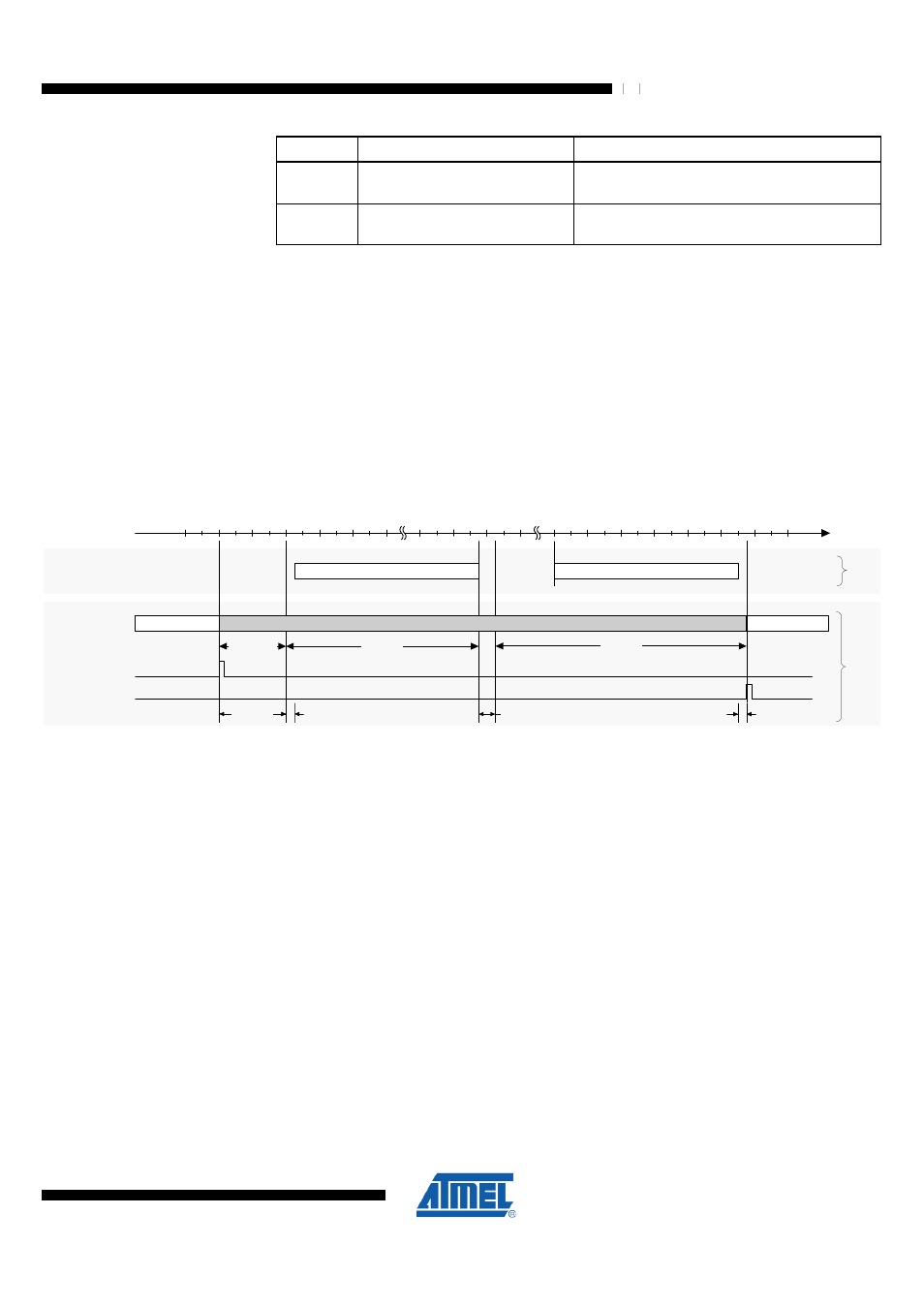

Figure 9-13. Example Timing of a TX_ARET Transaction

R

X

/T

X

F

ra

m

e

o

n

A

ir

TX_ARET_ON

BUSY_TX_ARET

TRX_STATE

FrameType

TX_ARET_ON

RX/TX

RX

RX_END

IRQ

Typ. Processing Delay

16 µs

672

0

x

time [µs]

128

x+352

SLPTR

TX

t

IRQ

Data Frame (Length = 10, ACK=1)

ACK Frame

32 µs

t

CSM A-CA

TX

CSMA-CA

RX

Note:

1. t

CSMA-CA

defines the random CSMA-CA processing time.

Here an example data frame of length 10 with an ACK request is transmitted, see

page 60. After the transmission the radio transceiver switches to receive mode

and expects an acknowledgement response. During the whole transaction including

frame transmit, wait for ACK and ACK receive the radio transceiver status register

TRX_STATUS signals BUSY_TX_ARET.

A successful reception of the acknowledgment frame is indicated by the

TRX24_TX_END interrupt. The status register TRX_STATUS changes back to

TX_ARET_ON. The TX_ARET status register TRAC_STATUS changes as well to

TRAC_STATUS = SUCCESS or TRAC_STATUS = SUCCESS_DATA_PENDING if the

frame pending subfield of the received ACK frame was set to 1.

9.4.2.6 Interrupt Handling

The interrupt handling in the Extended Operating Mode is similar to the Basic Operating

Mode (see section

page 38). The microcontroller enables

interrupts by setting the appropriate bit in register IRQ_MASK.

For RX_AACK and TX_ARET the following interrupts (

page 60) inform

about the status of a frame reception and transmission: