Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 120

120

8266A-MCU Wireless-12/09

ATmega128RFA1

specified in IEEE 802.15.4-2006. Reserved frame types are explained in IEEE 802.15.4

section 7.2.1.1.1. If AACK_FLTR_RES_FT = 0 a received, reserved frame is only

checked for a valid FCS.

•

Bit 4 – AACK_UPLD_RES_FT - Process Reserved Frames

If AACK_UPLD_RES_FT = 1 received frames indicated as reserved are further

processed. A RX_END interrupt is generated if the FCS of those frames is valid. In

conjunction with the configuration bit AACK_FLTR_RES_FT set, these frames are

handled like IEEE 802.15.4 compliant data frames during RX_AACK transaction. An

AMI interrupt is issued if the address in the received frame matches the node address.

That means if a reserved frame passes the third level filter rules, an acknowledgment

frame is generated and transmitted if it was requested by the received frame. If this is

not wanted bit AACK_DIS_ACK in register CSMA_SEED_1 has to be set.

•

Bit 3 – Res - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 2 – AACK_ACK_TIME - Reduce Acknowledgment Time

According to IEEE 802.15.4, section 7.5.6.4.2 the transmission of an acknowledgment

frame shall commence 12 symbols (aTurnaroundTime) after the reception of the last

symbol of a data or MAC command frame. This is achieved with the reset value of the

register bit AACK_ACK_TIME. If AACK_ACK_TIME = 1 an acknowledgment frame is

alternatively sent already 2 symbol periods (32 µs) after the reception of the last symbol

of a data or MAC command frame. This may be applied to proprietary networks or

networks using the High Data Rate Modes to increase battery lifetime and to improve

the overall data throughput. This setting affects also to acknowledgment frame

response time for slotted acknowledgment operation.

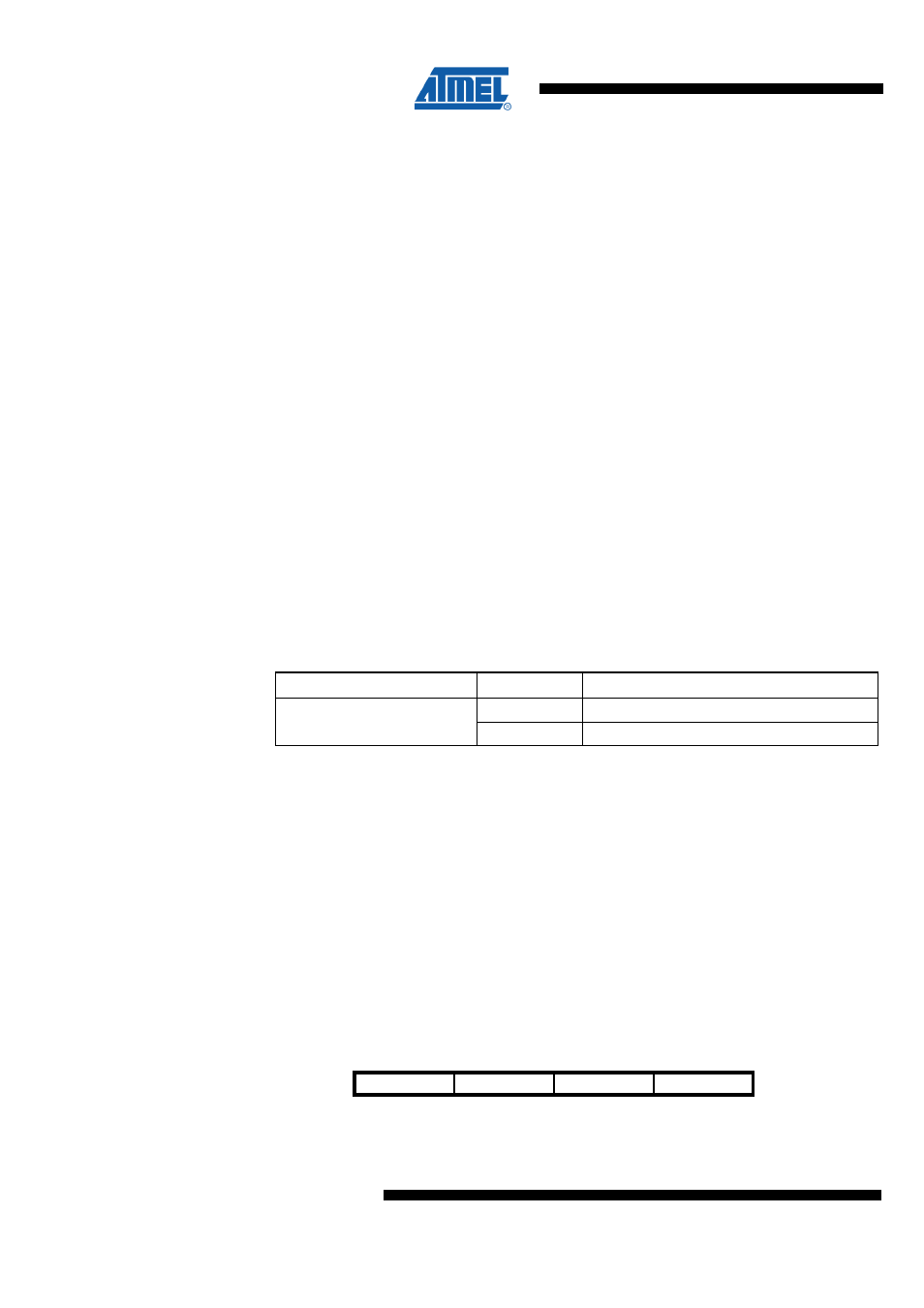

Table 9-61 AACK_ACK_TIME Register Bits

Register Bits

Value

Description

0

12 symbols acknowledgment time

AACK_ACK_TIME

1

2 symbols acknowledgment time

•

Bit 1 – AACK_PROM_MODE - Enable Promiscuous Mode

This register bit enables the promiscuous mode within the RX_AACK mode; refer to

IEEE 802.15.4-2006 chapter 7.5.6.5. If this bit is set, every incoming frame with a valid

PHR finishes with a RX_END interrupt even if the third level filter rules do not match or

the FCS is not valid. The bit RX_CRC_VALID of register PHY_RSSI is set accordingly.

If this bit is set and a frame passes the third level filter rules, an acknowledgment frame

is generated and transmitted unless disabled by bit AACK_DIS_ACK of register

CSMA_SEED_1.

•

Bit 0 – Res - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

9.12.25 FTN_CTRL – Transceiver Filter Tuning Control Register

Bit

7

6

5

4

NA ($158)

FTN_START

Resx6

Resx5

Resx4

FTN_CTRL

Read/Write

RW

RW

RW

RW

Initial Value

0

1

0

1