Table 27-3 on, Table 27-4 on, Table 27-5 on – Rainbow Electronics ATmega128RFA1 User Manual

Page 416: Figure 27-6 on, Atmega128rfa1

416

8266A-MCU Wireless-12/09

ATmega128RFA1

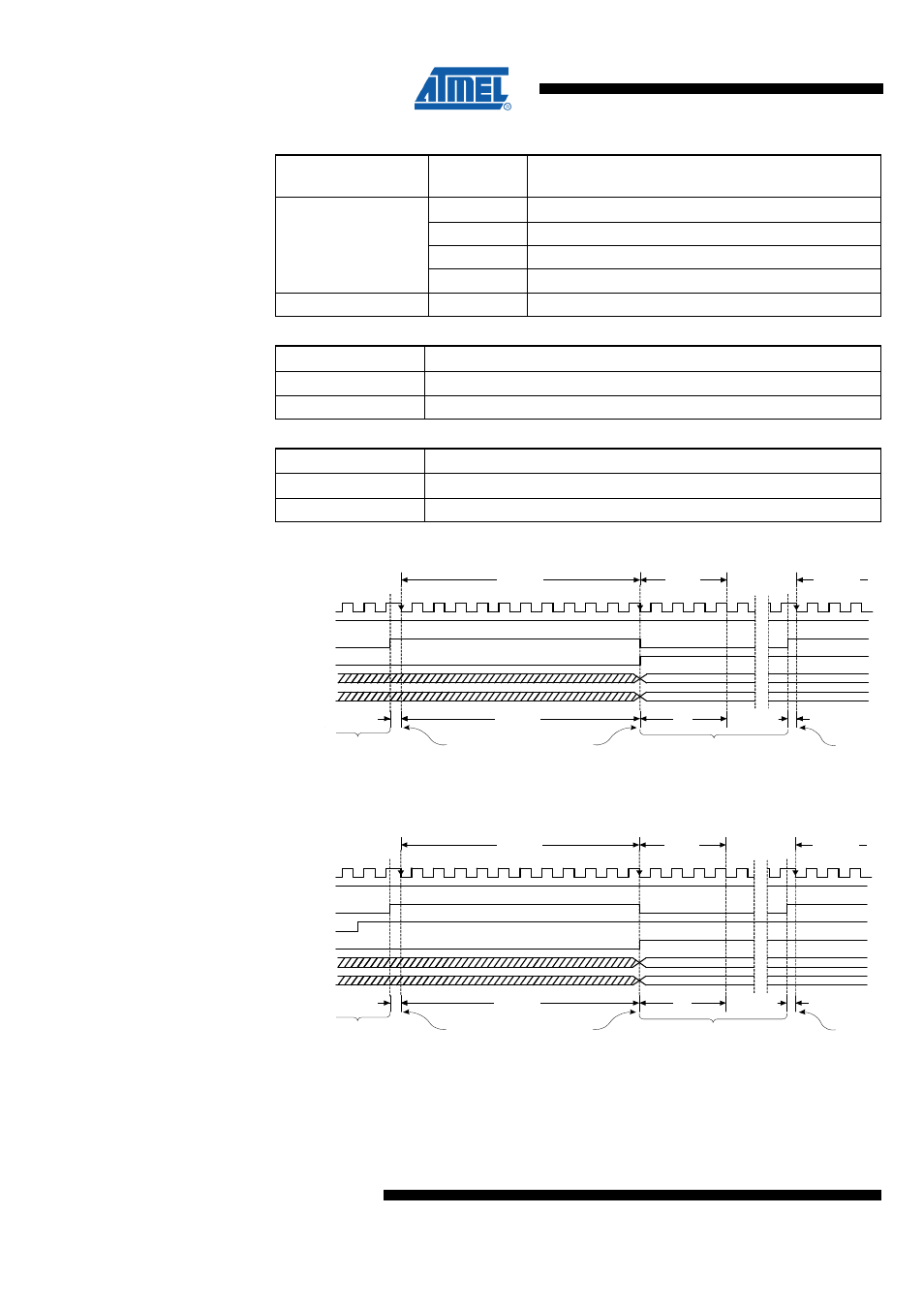

Table 27-3. Conversion Start Delay

Channel

ADPS

Delay from Conversion Start Request to Sample &

Hold t

SCSMP

0, 1

2 CPU clock cycles

2

4 CPU clock cycles

3

0 CPU clock cycles

Single-Ended

4…7

0 CPU clock cycles

Differential

0…7

2 ADC clock cycles

Table 27-4. Tracking Time

Channel

Tracking Phase Duration t

TRCK

in ADC Clock Cycles

Single-Ended

ADTHT+1, minimum 500 ns

Differential

2ADTHT+3

Table 27-5. Sample Rate in Free Running Mode

Channel

Sample Rate in ADC Clock Cycles

Single-Ended

ADTHT+12

Differential

2ADTHT+14

Figure 27-6. ADC Timing Diagram, Single Conversion

A D C C lo c k

A D E N

A D S C

A D IF

A D C H

A D C L

M U X a n d R E F S U p d a te

1 1 T

A D C _ C LK

t

T R C K

T ra c k in g

C o n ve rs io n

t

S C S M P

S ig n a n d M S B o f R e s u lt

L S B o f R e s u lt

M U X a n d R E F S U p d a te

C o n ve rs io n

C o m p le te

t

S C S M P

C o n ve rs io n

P re s ca le r R e s e t

a n d

S a m p le & H o ld

P re s ca le r

R e se t

a n d

S a m p le

& H o ld

Figure 27-7. ADC Timing Diagram, Auto Triggered Conversion

A D C C lo ck

A D E N

T rig g e r S o u rc e

A D IF

A D C H

A D C L

M U X a n d R E F S U p d a te

1 1 T

A D C _ C L K

t

T R C K

T ra c kin g

C o n v e rs io n

t

S C S M P

S ig n a n d M S B o f R e s u lt

L S B o f R e su lt

M U X a n d R E F S U p d a te

C o n ve rs io n

C o m p le te

t

S C S M P

C o n ve rs io n

P re s ca le r R e s e t

a n d

S a m p le & H o ld

A D A T E

P re s ca le r

R e se t

a n d

S a m p le

& H o ld