2 rx_aack mode timing, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 56

56

8266A-MCU Wireless-12/09

ATmega128RFA1

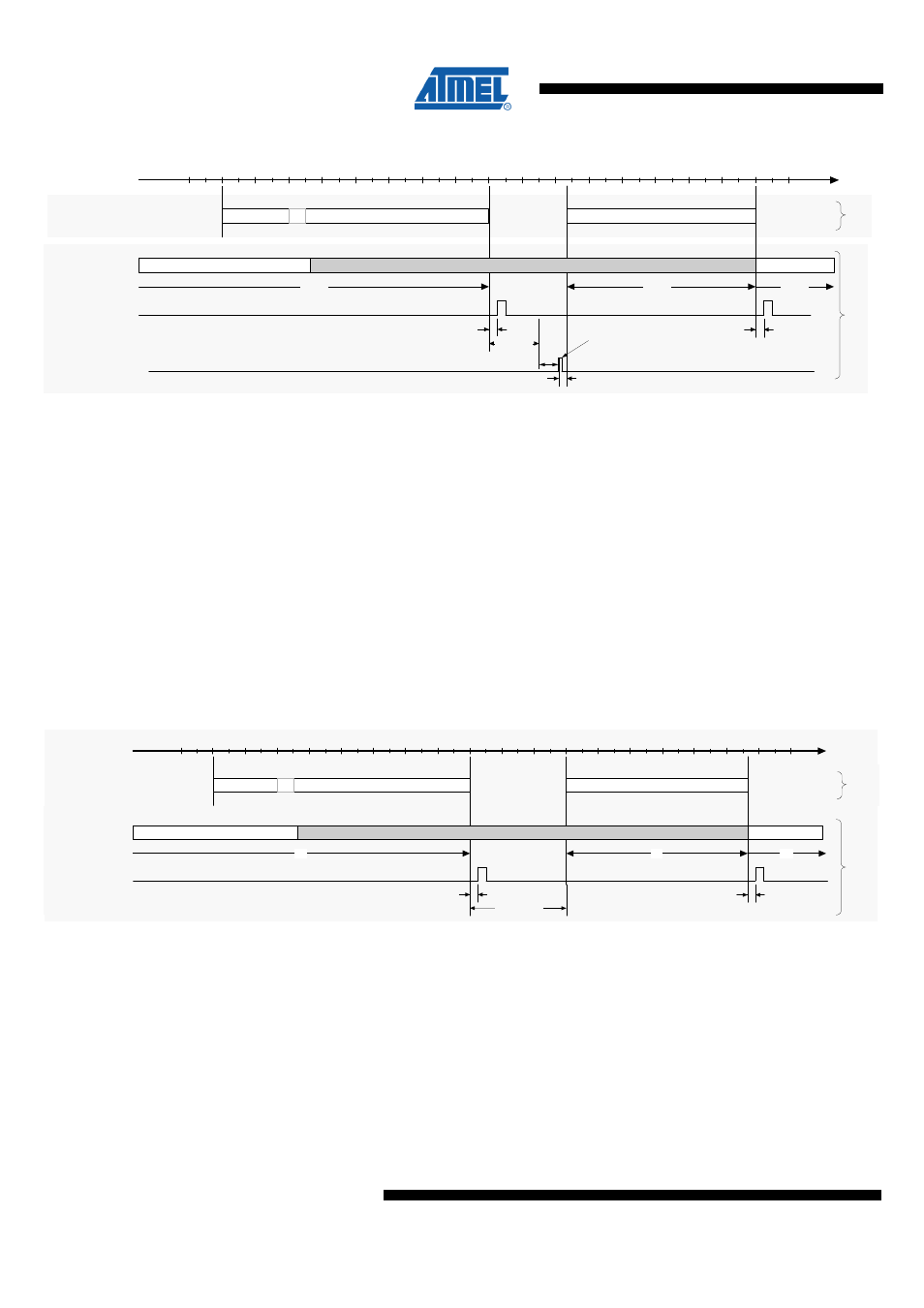

Figure 9-10. Example Timing of an RX_AACK Transaction for Slotted Operation

R

X

/T

X

F

ra

m

e

o

n

A

ir

R X _A A C K _O N

T R X _ S T A T E

F ram e T ype

R X _A A C K _O N

R X /TX

R X

TX

T R X 24_R X _E N D

IR Q

R X

T yp . P rocessing D elay

t

IR Q

51 2

0

7 04

tim e [µ s]

64

1 026

D ata Fram e (Length = 10, A C K = 1)

A C K F ram e

S F D

96 µ s

(6 sym bols)

S LP TR

t

T R 1 0

T X

R X

S LP T R

A C K transm ission initiated by m icrocontroller

B U S Y _R X _A A C K

R X

w aiting period signaled by register bits T R A C _S T A T U S

t

IR Q

T R X 24_T X _E N D

If bit AACK_ACK_TIME of register XAH_CTRL_1 is set, an acknowledgment frame can

be sent already 2 symbol times after the reception of the last symbol of a data or MAC

command frame.

9.4.2.4.2 RX_AACK Mode Timing

A timing example of an RX_AACK transaction is shown in the next figure. In this

example a data frame of length 10 with an ACK request is received. The radio

transceiver changes to state BUSY_RX_AACK after SFD detection. The completion of

the frame reception is indicated by a TRX24_RX_END interrupt. Interrupts

TRX24_RX_START and TRX24_AMI are disabled in this example. The ACK frame is

automatically transmitted after a default wait period of 12 symbols (192 µs), bit

AACK_ACK_TIME = 0 (reset value). The interrupt latency t

IRQ

is specified in section

"Digital Interface Timing Characteristics" on page 507

.

Figure 9-11. Example Timing of an RX_AACK Transaction

R

X

/T

X

F

ra

m

e

o

n

A

ir

R X _A A C K _O N

B U S Y _R X _A A C K

T R X _S T A T E

F ram e T ype

R X _A A C K _O N

R X /T X

R X

TX

TR X 24 _R X _E N D

IR Q

R X

T yp. P rocessing D elay

t

IR Q

5 1 2

0

7 0 4

tim e [µ s]

6 4

1 0 8 8

D ata F ram e (Length = 10, A C K = 1)

A C K F ram e

S F D

192 µ s

(12 sym bols)

TR X 24_ TX _E N D

t

IR Q

If bit AACK_ACK_TIME of register XAH_CTRL_1 is set, an acknowledgment frame is

sent already 2 symbol times after the reception of the last symbol of a data or MAC

command frame.