Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 202

202

8266A-MCU Wireless-12/09

ATmega128RFA1

TOSC2, Timer Oscillator pin 1: Setting the AS2 bit to one and the EXCLKAMR bit to

zero in ASSR, enables asynchronous clocking of Timer/Counter2 by a Crystal

Oscillator. The pin PG4 is disconnected from the port, and becomes the input of the

inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin,

and the pin can not be used as an I/O pin.

TOSC2 – Port G, Bit 3

TOSC2, Timer Oscillator pin 2: Setting the AS2 bit to one and the EXCLKAMR bit to

zero in ASSR, enables asynchronous clocking of Timer/Counter2 by a Crystal

Oscillator. The pin PG3 is disconnected from the port, and becomes the inverting output

of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and

the pin can not be used as an I/O pin.

•

AMR – Port G, Bit 2

AMR, Automated Meter Reading Input: Setting the AS2 and the EXCLKAMR bits in

ASSR to one, enables asynchronous clocking of Timer/Counter2 by the AMR pin

•

DIG1 – Port G, Bit 1

DIG1, Radio Transceiver Antenna Diversity

Control Output: If the bit

ANT_EXT_SW_EN in ANT_DIV is set to one then the PG1 pin serves as a Radio

Transceiver output to control External Antenna Diversity.

•

DIG3 – Port G, Bit 0

DIG3, Radio Transceiver RX/TX Indicator Output: If the bit PA_EXT_EN in

TRX_CTRL_1 is set to one then the PG0 pin serves as the Radio Transceiver

receive/transmit indicator output to control an external RF front-end.

relates the alternate functions of Port G to the overriding signals

.

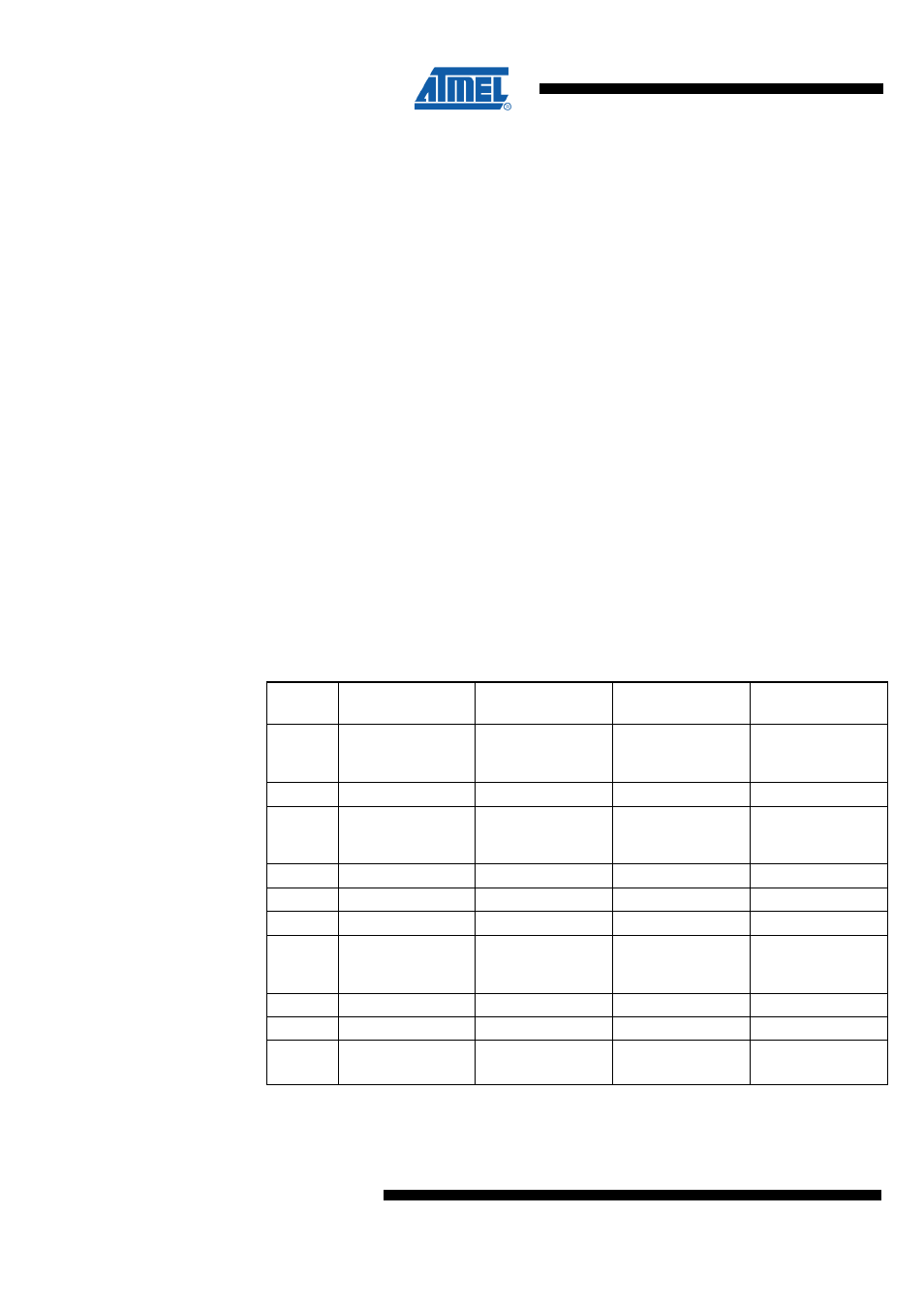

Table 14-16. Overriding Signals for Alternate Functions PG5:PG2

Signal

Name

PG5/OC0B

PG4/TOSC1

PG3/TOSC2

PG2/AMR

PUOE

–

AS2 &

(~EXCLKAMR)

AS2 &

(~EXCLKAMR) &

(~EXCLK)

AS2 & EXCLKAMR

PUOV

–

0

0

0

DDOE

–

AS2 &

(~EXCLKAMR)

AS2 &

(~EXCLKAMR) &

(~EXCLK)

AS2 & EXCLKAMR

DDOV

–

0

0

0

PVOE

OC0B Enable

0

0

0

PVOV

OC0B

0

0

0

DIEOE

–

AS2 &

(~EXCLKAMR)

AS2 &

(~EXCLKAMR) &

(~EXCLK)

AS2 & EXCLKAMR

DIEOV

–

EXCLK

0

1

DI

–

–

–

AMR

AIO

–

T/C2

OSC INPUT

T/C2

OSC OUTPUT

–