26 sccr1 - symbol counter control register 1, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 144

144

8266A-MCU Wireless-12/09

ATmega128RFA1

feature works only if the symbol counter module operates with the 16 MHz clock from

XTAL1. After switching to RTC clock source, the symbol period synchronization is lost.

This bit is cleared automatically.

•

Bit 6 – SCMBTS - Manual Beacon Timestamp

With this bit a manual beacon timestamp can be generated. If set to 1, the current

symbol counter value is stored into the beacon timestamp register. The bit is cleared

afterwards. The manual beacon timestamping can be used in conjunction with the

relative compare mode of the three compare units to generate compare match

interrupts without having a beacon frame received.

•

Bit 5 – SCEN - Symbol Counter enable

This bit activates the symbol counter module. If the bit is not set, the counter, backoff

slot counter and the compare unit are disabled and disconnected from the clock. In this

way the power consumption can be reduced. All registers can be accessed, but write

access to the counter register SCCNT is not possible.

•

Bit 4 – SCCKSEL - Symbol Counter Clock Source select

With this bit the clock source for the symbol counter can be selected. If the bit is one,

the RTC clock from TOSC1 is selected, otherwise the symbol counter operates with the

clock from XTAL1. During transceiver sleep modes the clock falls back to the RTC clock

source, regardless of the selected clock. After wakeup, it switches back to the previosly

selected clock source.

•

Bit 3 – SCTSE - Symbol Counter Automatic Timestamping enable

This bit enables automatic SFD and Beacon Timestamping. If the bit is zero, no

automatic timestamp capturing is possible. Only manual beacon timestamping can be

used.

•

Bit 2 – SCCMP3 - Symbol Counter Compare Unit 3 Mode select

This bit enables the relative compare mode for compare unit 3. If enabled, the counter

value is compared against the content of the beacon timestamp register plus the

content of the compare register 3 (SCCNT == SCBTS+SCOCR3). Otherwise, the

counter is compared against the copare register 3 (SCCNT == SCOCR3).

•

Bit 1 – SCCMP2 - Symbol Counter Compare Unit 2 Mode select

This bit enables the relative compare mode for compare unit 2. If enabled, the counter

value is compared against the content of the beacon timestamp register plus the

content of the compare register 2 (SCCNT == SCBTS+SCOCR2). Otherwise, the

counter is compared against the copare register 2 (SCCNT == SCOCR2).

•

Bit 0 – SCCMP1 - Symbol Counter Compare Unit 1 Mode select

This bit enables the relative compare mode for compare unit 1. If enabled, the counter

value is compared against the content of the beacon timestamp register plus the

content of the compare register 1 (SCCNT == SCBTS+SCOCR1). Otherwise, the

counter is compared against the copare register 1 (SCCNT == SCOCR1).

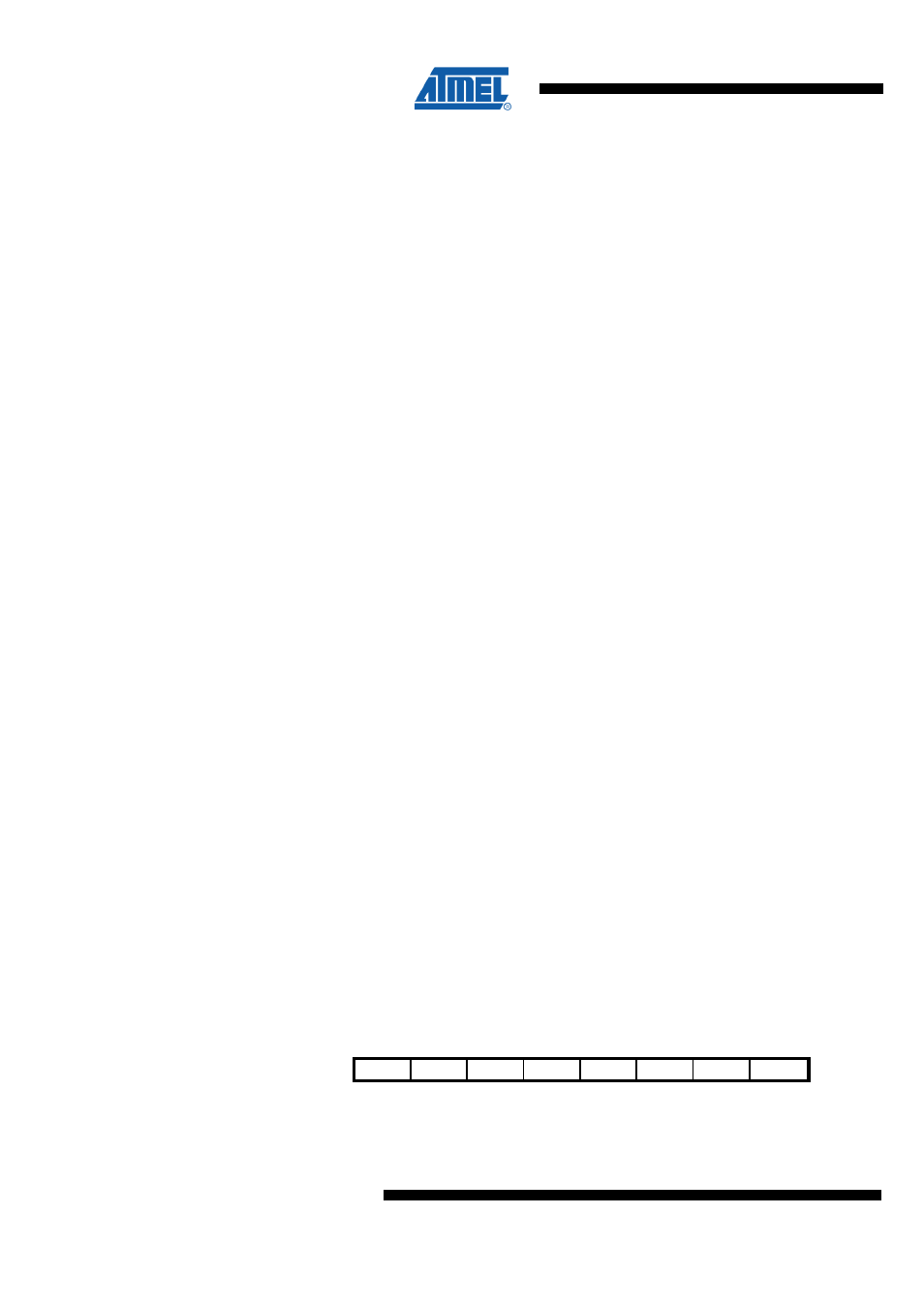

10.11.26 SCCR1 – Symbol Counter Control Register 1

Bit

7

6

5

4

3

2

1

0

NA ($DD)

Res6

Res5

Res4

Resx4

Resx3

Resx2

Resx1

SCENBO

SCCR1

Read/Write

R

R

R

RW

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

0

0