29 timsk3 - timer/counter3 interrupt mask register, 30 tifr3 - timer/counter3 interrupt flag register, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 284

284

8266A-MCU Wireless-12/09

ATmega128RFA1

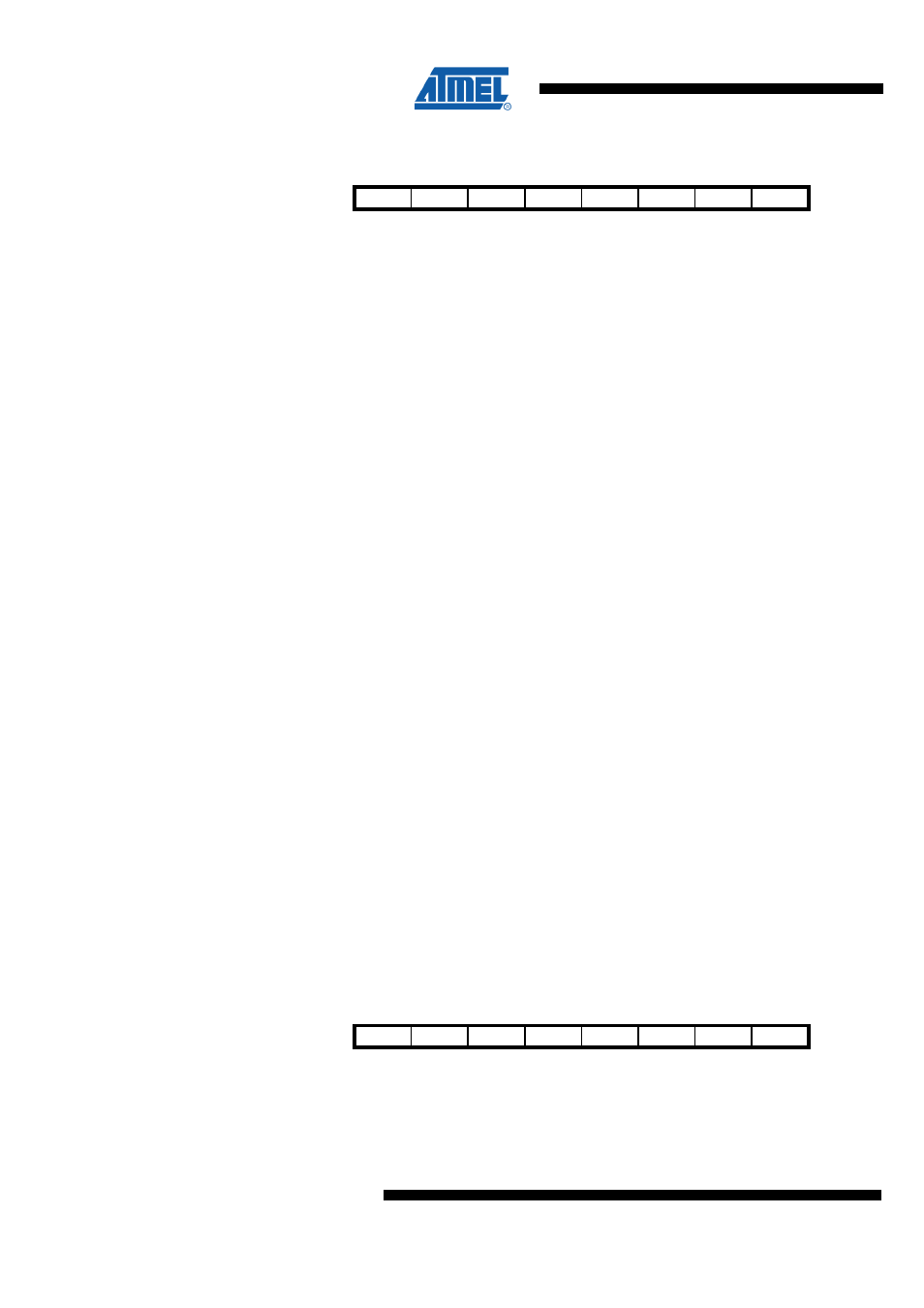

18.11.29 TIMSK3 – Timer/Counter3 Interrupt Mask Register

Bit

7

6

5

4

3

2

1

0

NA ($71)

Res1

Res0

ICIE3

Res

OCIE3C OCIE3B OCIE3A

TOIE3

TIMSK3

Read/Write

R

R

RW

R

R

R

RW

RW

Initial Value

0

0

0

0

0

0

0

0

•

Bit 7:6 – Res1:0 - Reserved Bit

This bit is reserved for future use. A read access always will return zero. A write access

does not modify the content.

•

Bit 5 – ICIE3 - Timer/Counter3 Input Capture Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts

globally enabled), the Timer/Counter3 Input Capture interrupt is enabled. The

corresponding Interrupt Vector is executed when the ICF3 Flag, located in TIFR3, is

set.

•

Bit 4 – Res - Reserved Bit

This bit is reserved for future use. A read access always will return zero. A write access

does not modify the content.

•

Bit 3 – OCIE3C - Timer/Counter3 Output Compare C Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts

globally enabled), the Timer/Counter3 Output Compare C Match interrupt is enabled.

The corresponding Interrupt Vector is executed when the OCF3C Flag, located in

TIFR3, is set.

•

Bit 2 – OCIE3B - Timer/Counter3 Output Compare B Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts

globally enabled), the Timer/Counter3 Output Compare B Match interrupt is enabled.

The corresponding Interrupt Vector is executed when the OCF3B Flag, located in

TIFR3, is set.

•

Bit 1 – OCIE3A - Timer/Counter3 Output Compare A Match Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts

globally enabled), the Timer/Counter3 Output Compare A Match interrupt is enabled.

The corresponding Interrupt Vector is executed when the OCF3A Flag, located in

TIFR3, is set.

•

Bit 0 – TOIE3 - Timer/Counter3 Overflow Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts

globally enabled), the Timer/Counter3 Overflow interrupt is enabled. The corresponding

Interrupt Vector is executed when the TOV3 Flag, located in TIFR3, is set.

18.11.30 TIFR3 – Timer/Counter3 Interrupt Flag Register

Bit

7

6

5

4

3

2

1

0

$18 ($38)

Res1

Res0

ICF3

Res

OCF3C

OCF3B

OCF3A

TOV3

TIFR3

Read/Write

R

R

RW

R

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

0

0

•

Bit 7:6 – Res1:0 - Reserved Bit