Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 332

332

8266A-MCU Wireless-12/09

ATmega128RFA1

control logic will sample the incoming signal of the SCK pin. To ensure correct sampling

of the clock signal, the minimum low and high periods should be:

Low period:

longer than 2 CPU clock cycles

High period:

longer than 2 CPU clock cycles

When the SPI is enabled, the data direction of the MOSI, MISO, SCK, and SS

__

pins is

overridden according to Table 21-1. For more details on automatic port overrides, refer

to

"Alternate Port Functions" on page 191

.

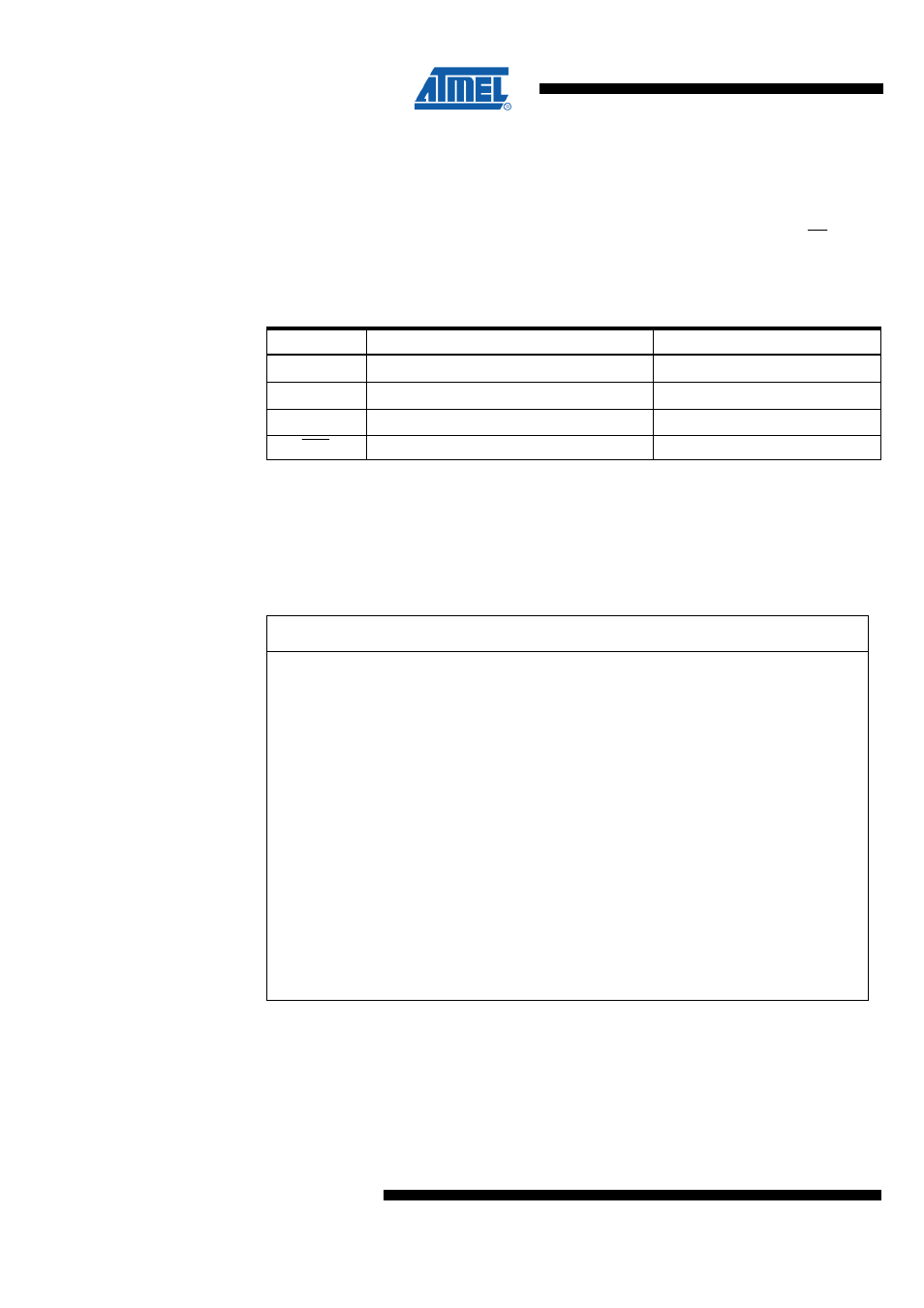

Table 22-1. Pin Overrides

(1)

Pin

Direction, Master SPI

Direction, Slave SPI

MOSI

User Defined

Input

MISO

Input

User Defined

SCK

User Defined

Input

SS

User Defined

Input

Note:

1. See

"Alternate Functions of Port B" on page 192

for a detailed description of how

to define the direction of the user defined SPI pins.

The following code examples show how to initialize the SPI as a Master and how to

perform a simple transmission. DDR_SPI in the examples must be replaced by the

actual Data Direction Register controlling the SPI pins. DD_MOSI, DD_MISO and

DD_SCK must be replaced by the actual data direction bits for these pins. E.g. if MOSI

is placed on pin PB5, replace DD_MOSI with DDB5 and DDR_SPI with DDRB.

Assembly Code Example

(

1

)

SPI_MasterInit:

; Set MOSI and SCK output, all others input

ldi r17,(1< out DDR_SPI,r17 ; Enable SPI, Master, set clock rate fck/16 ldi r17,(1< out SPCR,r17 ret SPI_MasterTransmit: ; Start transmission of data (r16) out SPDR,r16 Wait_Transmit: ; Wait for transmission complete sbis SPSR,SPIF rjmp Wait_Transmit ret