3 address packet format, 4 data packet format – Rainbow Electronics ATmega128RFA1 User Manual

Page 379

379

8266A-MCU Wireless-12/09

ATmega128RFA1

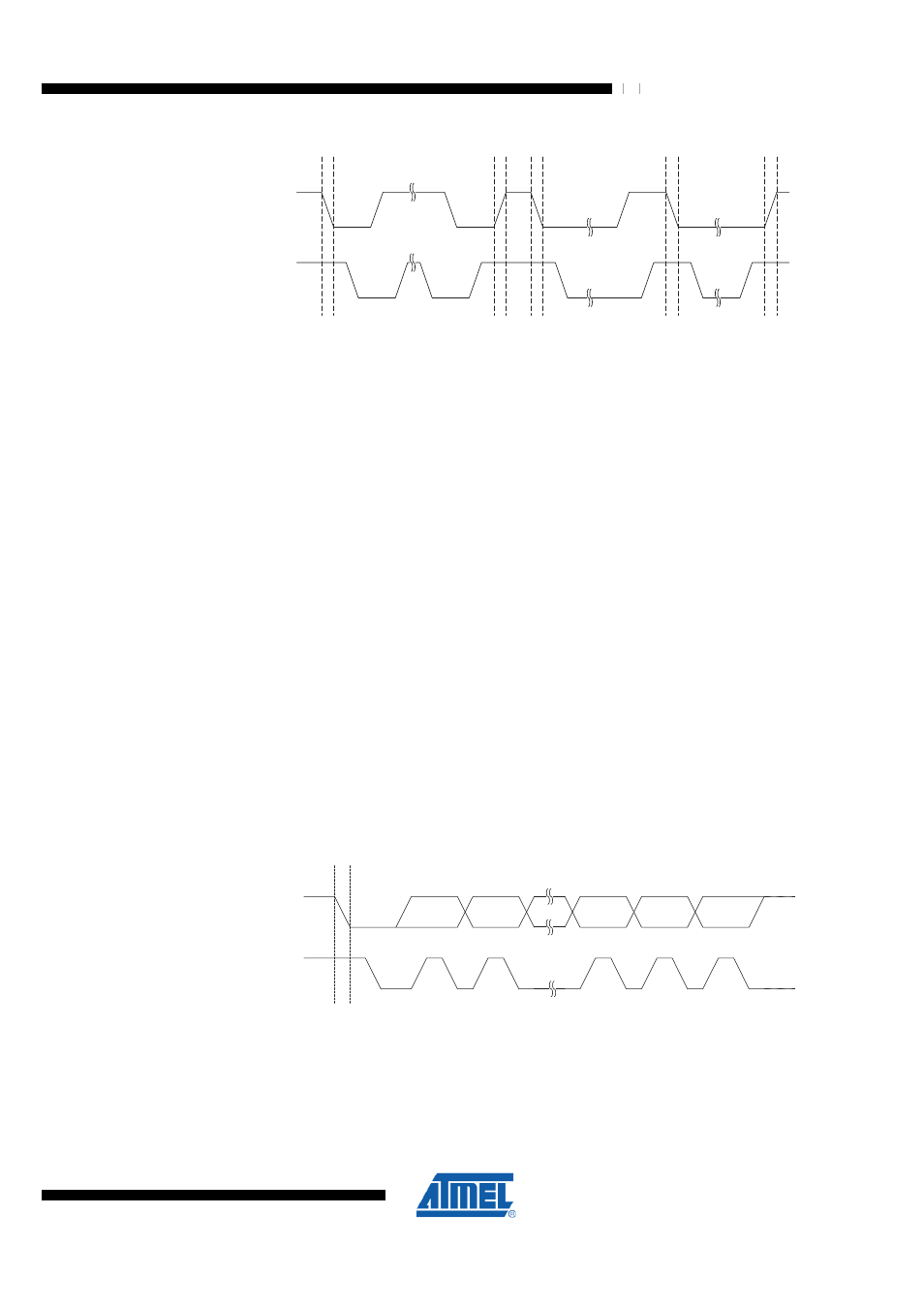

Figure 25-3. START, REPEATED START and STOP conditions

SDA

SCL

START

STOP

REPEATED START

STOP

START

25.3.3 Address Packet Format

All address packets transmitted on the TWI bus are 9 bits long, consisting of 7 address

bits, one READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is

set, a read operation is to be performed, otherwise a write operation should be

performed. When a Slave recognizes that it is being addressed, it should acknowledge

by pulling SDA low in the ninth SCL (ACK) cycle. If the addressed Slave is busy, or for

some other reason can not service the Master’s request, the SDA line should be left

high in the ACK clock cycle. The Master can then transmit a STOP condition, or a

REPEATED START condition to initiate a new transmission. An address packet

consisting of a slave address and a READ or a WRITE bit is called SLA+R or SLA+W,

respectively.

The MSB of the address byte is transmitted first. Slave addresses can freely be

allocated by the designer, but the address 0000 000 is reserved for a general call.

When a general call is issued, all slaves should respond by pulling the SDA line low in

the ACK cycle. A general call is used when a Master wishes to transmit the same

message to several slaves in the system. When the general call address followed by a

Write bit is transmitted on the bus, all slaves set up to acknowledge the general call will

pull the SDA line low in the ack cycle. The following data packets will then be received

by all the slaves that acknowledged the general call. Note that transmitting the general

call address followed by a Read bit is meaningless, as this would cause contention if

several slaves started transmitting different data.

All addresses of the format 1111 xxx should be reserved for future purposes.

Figure 25-4. Address Packet Format

SDA

SCL

START

1

2

7

8

9

Addr MSB

Addr LSB

R/W

ACK

25.3.4 Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data

byte and an acknowledge bit. During a data transfer, the Master generates the clock

and the START and STOP conditions, while the Receiver is responsible for

acknowledging the reception. An Acknowledge (ACK) is signaled by the Receiver