6 output compare unit – Rainbow Electronics ATmega128RFA1 User Manual

Page 316

316

8266A-MCU Wireless-12/09

ATmega128RFA1

•

OCR2A changes its value from MAX, like in

. When the

OCR2A value is MAX the OCn pin value is the same as the result of a down-

counting compare match. To ensure symmetry around BOTTOM the OCn value at

MAX must correspond to the result of an up-counting Compare Match.

•

The timer starts counting from a value higher than the one in OCR2A, and for that

reason misses the Compare Match and hence the OCn change that would have

happened on the way up.

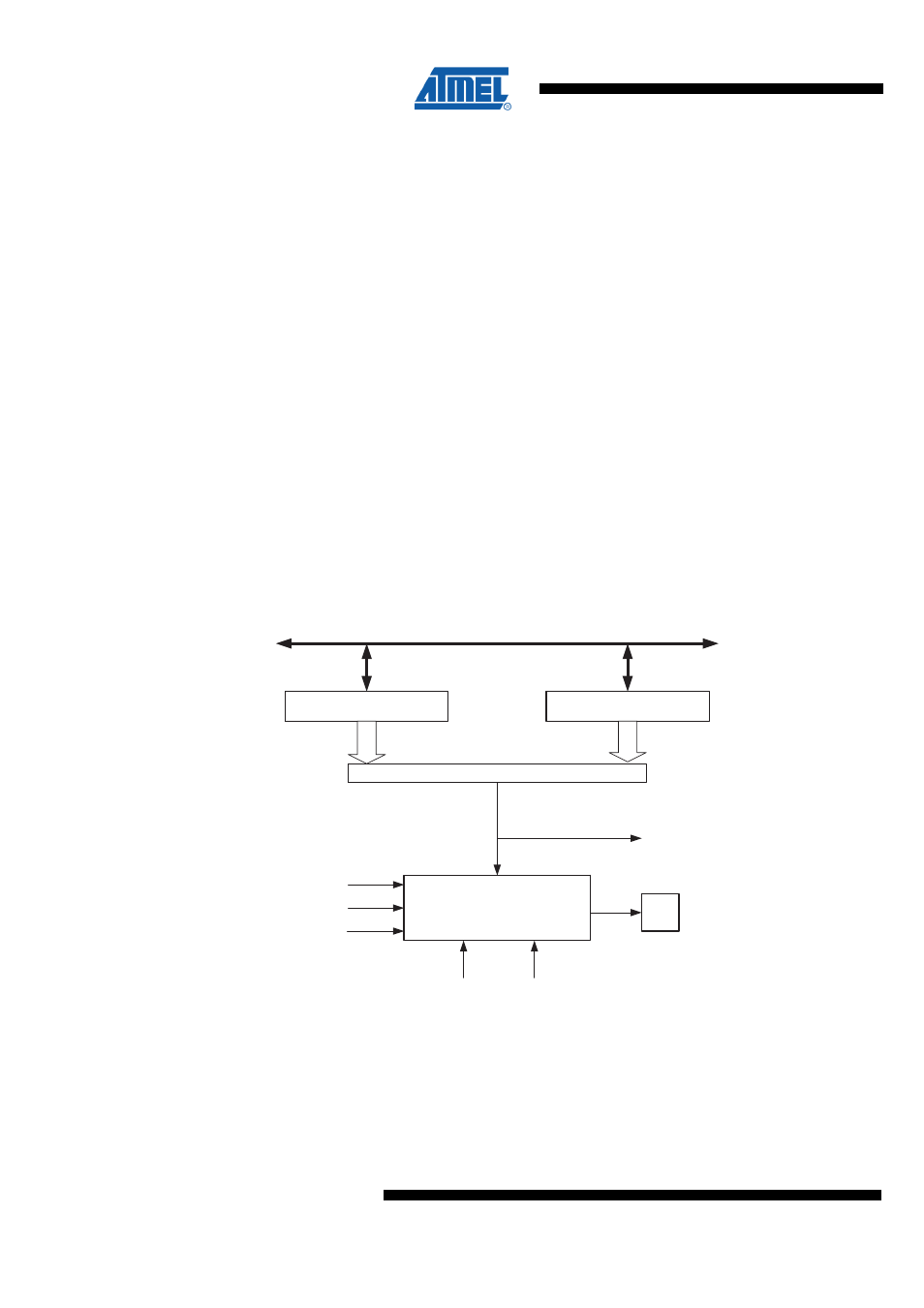

21.6 Output Compare Unit

The 8 bit comparator continuously compares TCNT2 with the Output Compare Register

(OCR2A and OCR2B). Whenever TCNT2 equals OCR2A or OCR2B, the comparator

signals a match. A match will set the Output Compare Flag (OCF2A or OCF2B) at the

next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare

Flag generates an Output Compare interrupt. The Output Compare Flag is

automatically cleared when the interrupt is executed. Alternatively, the Output Compare

Flag can be cleared by software by writing a logical one to its I/O bit location. The

Waveform Generator uses the match signal to generate an output according to

operating mode set by the WGM22:0 bits and Compare Output mode (COM2x1:0) bits.

The max and bottom signals are used by the Waveform Generator for handling the

special cases of the extreme values in some modes of operation (chapter

).

shows a block diagram of the Output Compare unit.

Figure 21-6. Output Compare Unit, Block Diagram

OCFn (Int.Req.)

=

(8-bit Comparator )

OCRn

OCxy

DATA BUS

TCNTn

WGMn1:0

Waveform Generator

top

FOCn

COMn1:0

bottom

The OCR2x Register is double buffered when using any of the Pulse Width Modulation

(PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of

operation, the double buffering is disabled. The double buffering synchronizes the

update of the OCR2x Compare Register to either top or bottom of the counting

sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical

PWM pulses, thereby making the output glitch-free.