8 clock output buffer, 9 timer/counter oscillator, 10 system clock prescaler – Rainbow Electronics ATmega128RFA1 User Manual

Page 152: System clock prescaler" on, Atmega128rfa1

152

8266A-MCU Wireless-12/09

ATmega128RFA1

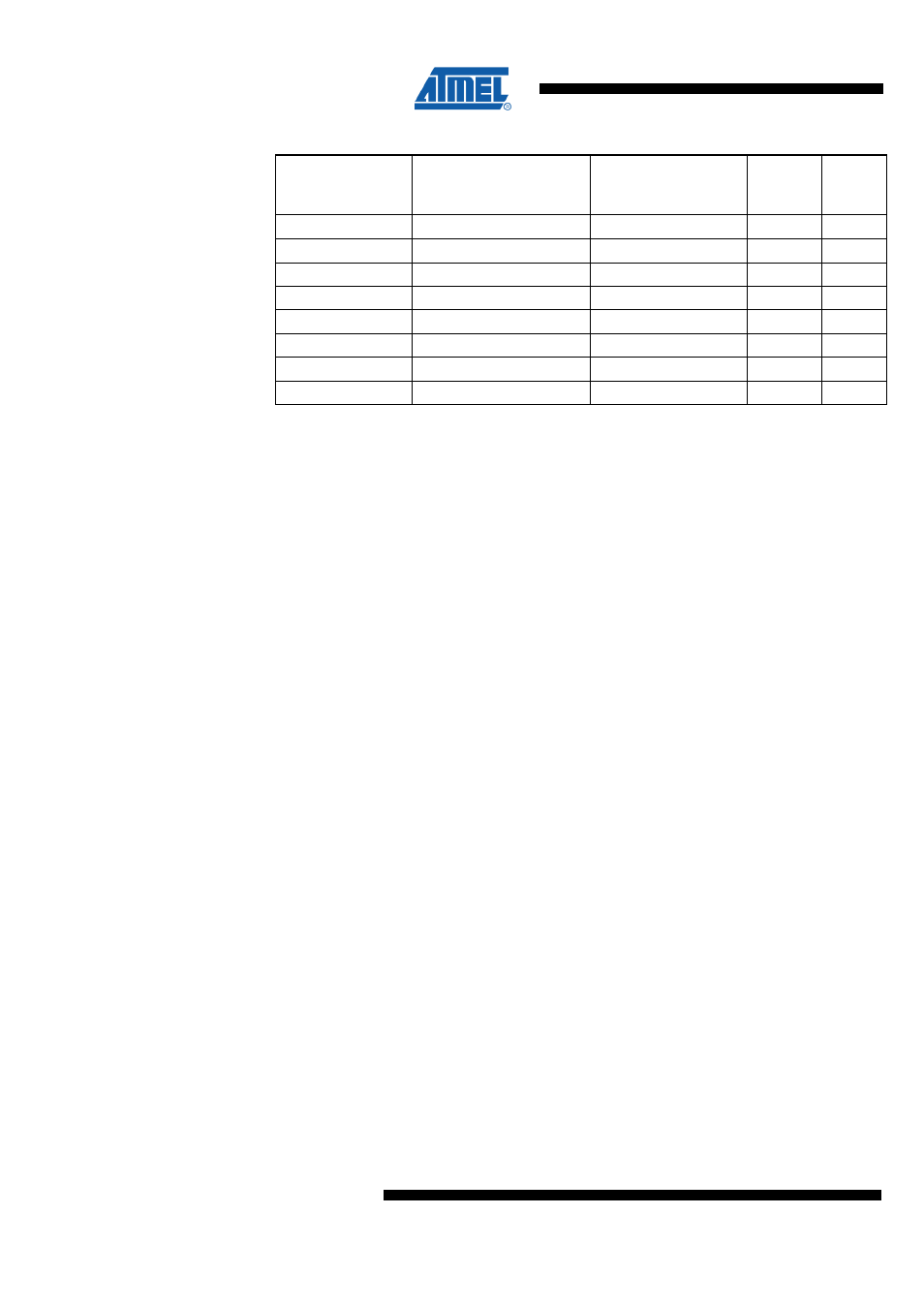

Table 11-10. Start-up Times for the Transceiver Oscillator Clock Selection

Power Conditions

Start-up Time from

Power-down and

Power-save

Additional Delay

from Reset

CKSEL0

SUT1:0

fast rising power

258 CK

14CK + 4.1 ms

0

00

slowly rising power

258 CK

14CK + 65 ms

0

01

BOD enabled

1K CK

14CK + 0 ms

0

10

fast rising power

1K CK

14CK + 4.1 ms

0

11

slowly rising power

1K CK

14CK + 65 ms

1

00

BOD enabled

16K CK

14CK + 0 ms

1

01

fast rising power

16K CK

14CK + 4.1 ms

1

10

slowly rising power

16K CK

14CK + 65 ms

1

11

11.8 Clock Output Buffer

The device can output the system clock on the CLKO pin. To enable the output, the

CKOUT Fuse has to be programmed. This mode is suitable when the chip clock is used

to drive other circuits on the system. The clock also will be output during reset, and the

normal operation of I/O pin will be overridden when the fuse is programmed. Any clock

source, including the internal RC Oscillator, can be selected when the clock is output on

CLKO. If the System Clock Prescaler is used, it is the divided system clock that is

output.

Special attention is required to prevent unwanted radiation from the connected PCB

clock trace. Proper filtering can help to suppress higher harmonics.

11.9 Timer/Counter Oscillator

The device can operate the Timer/Counter2 from the 32.768 kHz crystal oscillator or an

external clock source. See section

"Application Circuits" on page 493

for the watch

crystal connection.

11.10 System Clock Prescaler

The ATmega128RFA1 has a system clock prescaler, and the system clock can be

divided by setting the “CLKPR – Clock Prescale Register”. This feature can be used to

decrease the system clock frequency and the power consumption when the

requirement for processing power is low. This can be used with all clock source options,

and it will affect the clock frequency of the CPU and all synchronous peripherals. The

clocks clk

I/O

, clk

ADC

, clk

CPU

, and clk

FLASH

are divided by a factor as shown in

Clock Prescale Register on page 154

.

The prescaler clock division factor of the internal RC-Oscillator is different from all other

clock sources, see register description

CLKPR – Clock Prescale Register on page 154

Flash, EEPROM, Fuse- and Lock-bit programming is not allowed while using RC-

Oscillator with CLKPS=0xF (clk

CPU

= 16MHz).

When switching between prescaler settings, the System Clock Prescaler ensures that

no glitches occur in the clock system. It also ensures that no intermediate frequency is

higher than neither the clock frequency corresponding to the previous setting nor the

clock frequency corresponding to the new setting.

The prescaler is implemented as a ripple counter running at the frequency of the

undivided clock, which may be faster than the CPU's clock frequency. Hence, it is not