Xah_ctrl_1, Transceiver, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 119

119

8266A-MCU Wireless-12/09

ATmega128RFA1

This register controls the sensitivity threshold of the receiver.

•

Bit 7 – RX_PDT_DIS - Prevent Frame Reception

RX_PDT_DIS = 1 prevents the reception of a frame even if the radio transceiver is in

receive modes. An ongoing frame reception is not affected. This operation mode is

independent of the setting of register bits RX_PDT_LEVEL.

•

Bit 6:4 – Res2:0 - Reserved

•

Bit 3:0 – RX_PDT_LEVEL3:0 - Reduce Receiver Sensitivity

These register bits reduce the receiver sensitivity such that frames with a RSSI level

below the RX_PDT_LEVEL threshold level are not received (RX_PDT_LEVEL>0). The

threshold level can be calculated according to the following formula: RX_THRES >

RSSI_BASE_VAL+3·(RX_PDT_LEVEL-1), for RX_PDT_LEVEL>0. If register bits

RX_PDT_LEVEL>0 the current consumption of the receiver in states RX_ON and

RX_AACK_ON is reduced by 500 µA. If register bits RX_PDT_LEVEL=0 (reset value)

all frames with a valid SHR and PHR are received, independently of their signal

strength. Examples for certain register settings are given in the following table.

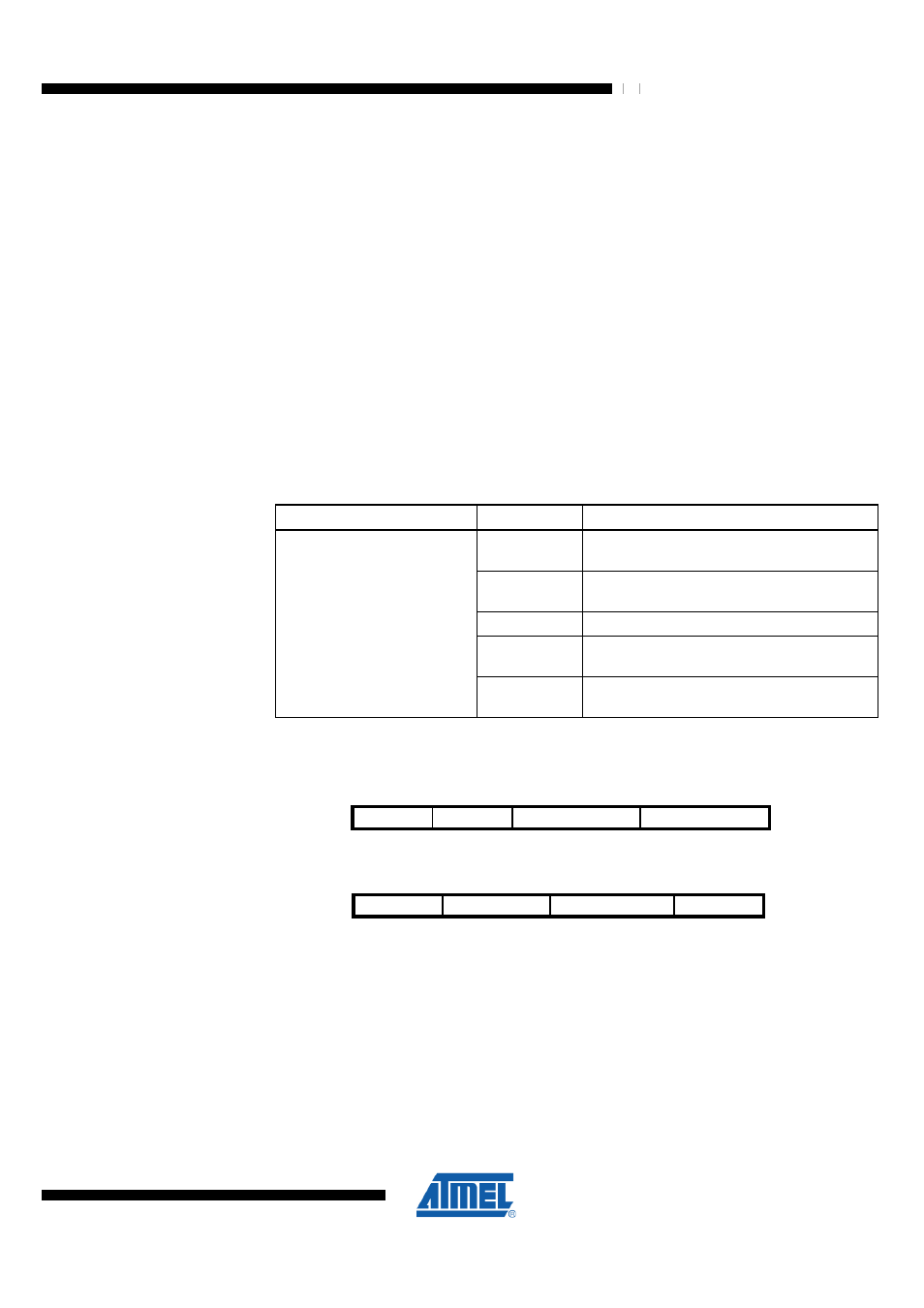

Table 9-60 RX_PDT_LEVEL Register Bits

Register Bits

Value

Description

0x0

RX_THRES ≤ RSSI_BASE_VAL (Reset

value); RSSI value not considered

0x1

RX_THRES > RSSI_BASE_VAL + 0 · 3;

RSSI > -90 dBm

0x2

...

0xE

RX_THRES > RSSI_BASE_VAL + 13 · 3;

RSSI > -51 dBm

RX_PDT_LEVEL3:0

0xF

RX_THRES > RSSI_BASE_VAL + 14 · 3;

RSSI > -48 dBm

9.12.24 XAH_CTRL_1 – Transceiver Acknowledgment Frame Control Register 1

Bit

7

6

5

4

NA ($157)

Res1

Res0

AACK_FLTR_RES_FT AACK_UPLD_RES_FT

XAH_CTRL_1

Read/Write

R

R

RW

RW

Initial Value

0

0

0

0

Bit

3

2

1

0

NA ($157)

Res

AACK_ACK_TIME AACK_PROM_MODE

Res

XAH_CTRL_1

Read/Write

R

RW

RW

R

Initial Value

0

0

0

0

This register is a multi-purpose control register for various RX_AACK settings.

•

Bit 7:6 – Res1:0 - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 5 – AACK_FLTR_RES_FT - Filter Reserved Frames

This register bit shall only be set if AACK_UPLD_RES_FT = 1. If

AACK_FLTR_RES_FT = 1 reserved frame types are filtered similar to data frames as