27 scsr - symbol counter status register, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 145

145

8266A-MCU Wireless-12/09

ATmega128RFA1

This register is used to enable the backoff slot counter.

•

Bit 7:5 – Res6:4 - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 4:1 – Resx4:1 - Reserved

•

Bit 0 – SCENBO - Backoff Slot Counter enable

If this bit is set, the backoff slot counter starts working. To enable the corresponding

IRQ the SCIRQM register must be updated.

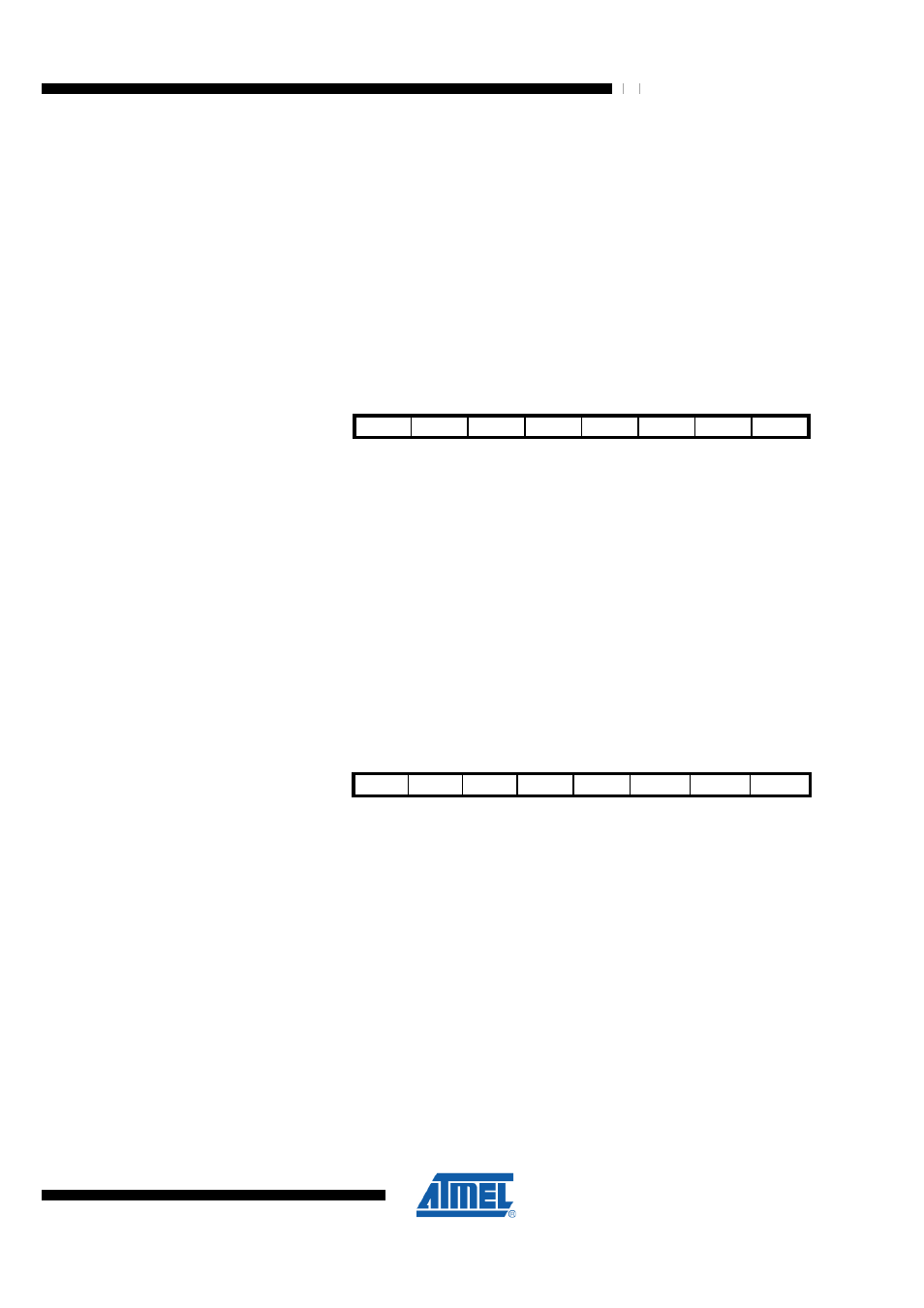

10.11.27 SCSR – Symbol Counter Status Register

Bit

7

6

5

4

3

2

1

0

NA ($DE)

Res6

Res5

Res4

Res3

Res2

Res1

Res0

SCBSY

SCSR

Read/Write

R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

•

Bit 7:1 – Res6:0 - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 0 – SCBSY - Symbol Counter busy

This bit is set if a write operation to the symbol counter register is pending. This bit is

set after writing the counter low byte (SCCNTLL) until the symbol counter is updated

with the new value. This update process can take up to 16 µs and during this time no

read or write access to the 32 bit counter register should occure.

10.11.28 SCIRQS – Symbol Counter Interrupt Status Register

Bit

7

6

5

4

3

2

1

0

NA ($E0)

Res2

Res1

Res0

IRQSBO IRQSOF IRQSCP3 IRQSCP2 IRQSCP1

SCIRQS

Read/Write

R

R

R

RW

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

0

0

The Interrupt Status Register indicates pending interrupt requests. If the corresponding

interrupt mask bit is set, an interrupt service routine is called and the status bit is

cleared automatically. It is also possible to clear the status bit by writing "1" to the

selected bit.

•

Bit 7:5 – Res2:0 - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 4 – IRQSBO - Backoff Slot Counter IRQ

This interrupt is generated every 320 µs, that means every 20 symbols.

•

Bit 3 – IRQSOF - Symbol Counter Overflow IRQ

This interrupt is generated when the 32 bit counter turns from 0xFFFFFFF to

0x00000000.

•

Bit 2 – IRQSCP3 - Compare Unit 3 Compare Match IRQ